# THESE

*présentée à*

**Institut National Polytechnique de Grenoble**

*pour obtenir le grade de*

Docteur de 3ème cycle

Génie Informatique

*par*

**Jean-Pierre SCHOELLKOPF**

**MACHINE PASC-HLL : DEFINITION D'UNE ARCHITECTURE

PIPE-LINE POUR UNE UNITE CENTRALE ADAPTEE

AU LANGAGE PASCAL.**

Thèse soutenue le 28 juin 1977 devant la Commission d'Examen :

Président : L. BOLLIET

Examinateurs : F. ANCEAU

C. GIRAUT

Ph. JORRAND

C. OTRAGE

## TABLE DES MATIERES

|                                                                                                                                                 | pages |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| <u>AVANT PROPOS</u>                                                                                                                             | 1     |

| <u>PREMIERE PARTIE</u>                                                                                                                          | 6     |

| <u>CHAPITRE 1 - Les aspects "système" de PASC-HLL</u>                                                                                           | 7     |

| A - INTRODUCTION                                                                                                                                | 8     |

| I - Multiprogrammation fonctionnelle                                                                                                            | 9     |

| II - Réalisation du partage des programmes                                                                                                      | 10    |

| B - L'ESPACE D'ADRESSAGE DE LA MACHINE                                                                                                          | 15    |

| I - Structuration de l'espace d'adressage                                                                                                       | 15    |

| II - Adressage des quatre zones de l'espace virtuel                                                                                             | 16    |

| III - Organisation des zones code et externe                                                                                                    | 20    |

| IV - Organisation de la zone contexte                                                                                                           | 30    |

| V - Organisation de la zone dynamique                                                                                                           | 33    |

| C - LES ENTREES-SORTIES                                                                                                                         | 35    |

| I - Structure des informations                                                                                                                  | 35    |

| II - Exécution des opérations d'entrée-sortie                                                                                                   | 37    |

| III - Les entrées-sorties évoluées                                                                                                              | 41    |

| IV - Conclusion sur les entrées-sorties                                                                                                         | 48    |

| <u>CHAPITRE 2 - Présentation générale de l'architecture de PASC-HLL</u>                                                                         | 49    |

| A - Définition d'un code machine adapté à la compilation et<br>à l'exécution du langage PASCAL                                                  | 50    |

| B - Définition d'un mécanisme d'exécution en pipeline d'un<br>code-machine de type post-fixé utilisant une file<br>d'attente plutôt qu'une pile | 61    |

| I - Introduction                                                                                                                                | 61    |

| II - Instruction d'un modèle pour une chaîne post-fixée                                                                                         | 66    |

| 1. définition                                                                                                                                   | 66    |

| 2. algorithme de gestion des trous                                                                                                              | 75    |

| 3. évaluation du taux d'extra-ordres                                                                                                            | 79    |

| III - Introduction d'un processeur de gestion de la file                                                                                        | 81    |

| 1. formalisation du problème des dépendances                                                                                                    | 82    |

| 2. expression du problème de l'anticipation                                                                                                     | 85    |

| IV - Conclusion                                                                                                                                 | 90    |

|                                                                        |     |

|------------------------------------------------------------------------|-----|

| <u>DEUXIEME PARTIE</u>                                                 | 91  |

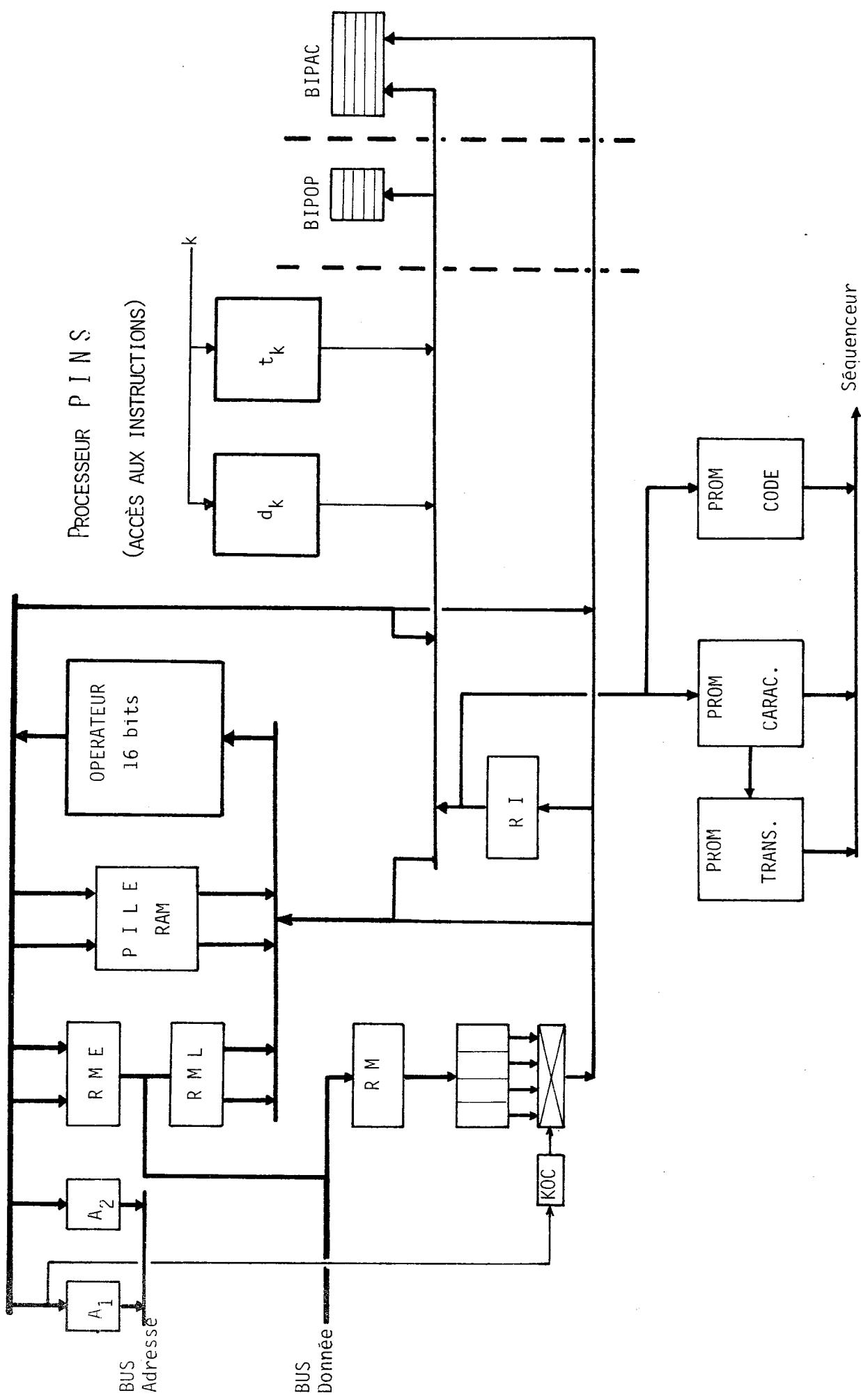

| <u>CHAPITRE 3 - Le processeur de traitement des instructions: PINS</u> | 94  |

| A - Introduction                                                       | 95  |

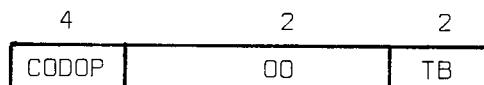

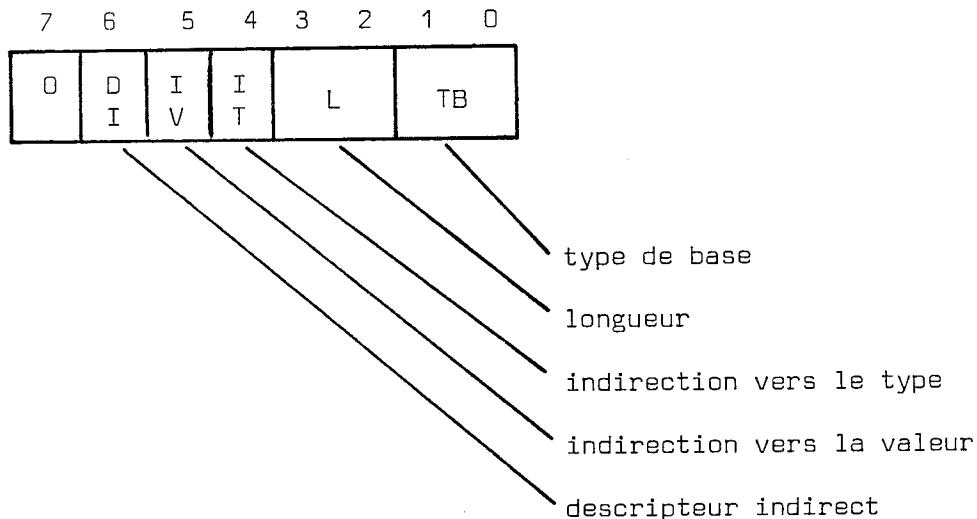

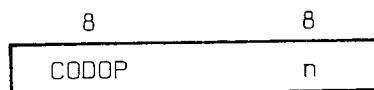

| I - Le codage des instructions                                         | 98  |

| II - Gestion d'une mémoire locale en pile                              | 100 |

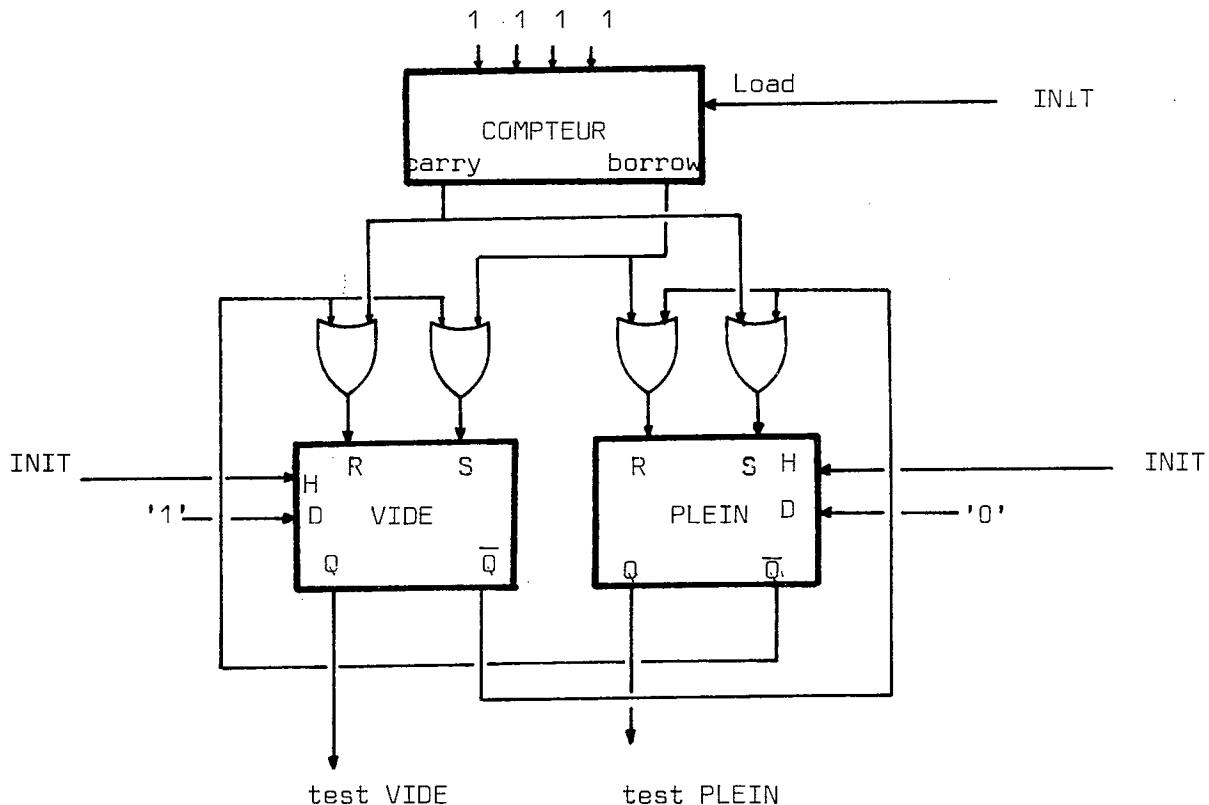

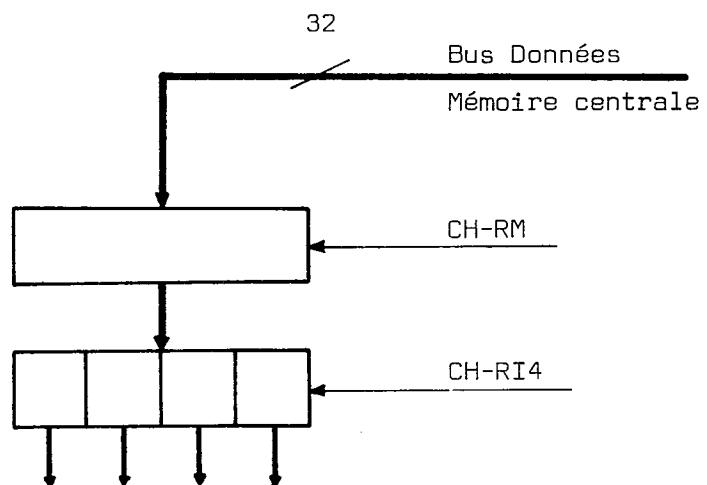

| B - Le module d'accès aux instructions                                 | 104 |

| I - Principe du module d'accès                                         | 104 |

| II - Contrôle du module d'accès                                        | 105 |

| III - Gestion de l'adresse de l'instruction suivante                   | 106 |

| C - Analyse de la chaîne post-fixée                                    | 109 |

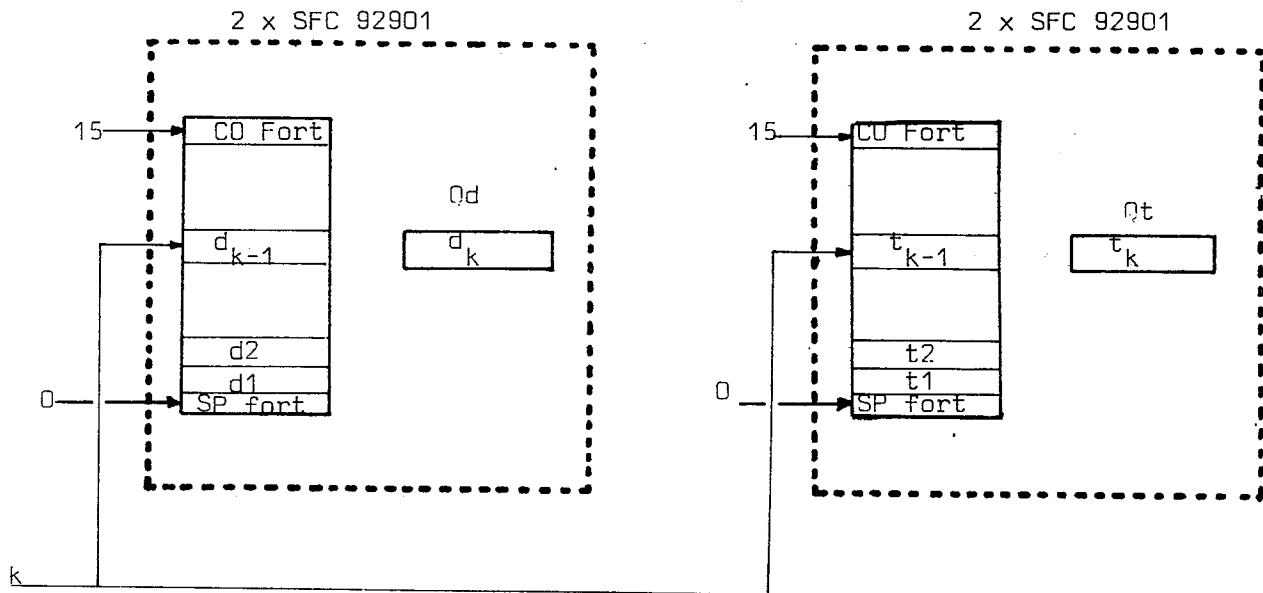

| I - Implantation des suites $\{d_k\}$ et $\{t_k\}$                     | 109 |

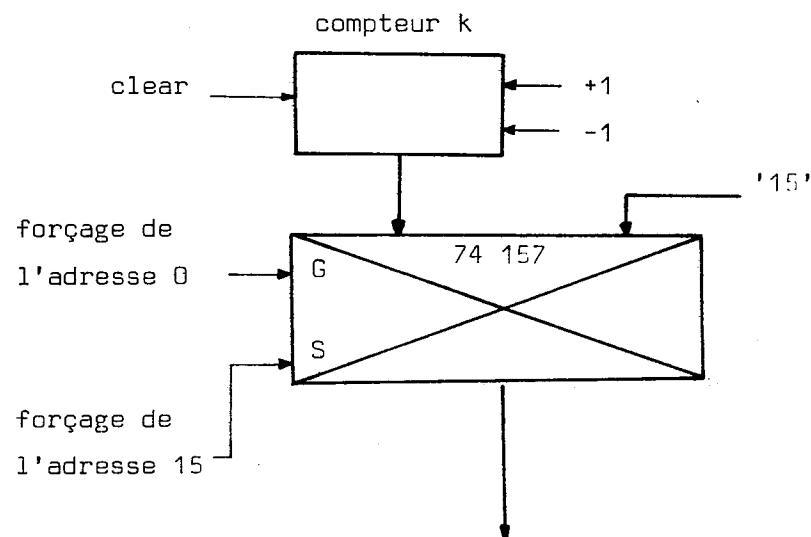

| II - Réalisation des algorithmes de gestion de la file                 | 111 |

| III - Exécution des instructions de contrôle                           | 120 |

| D - Conclusion                                                         | 130 |

| <u>CHAPITRE 4 - Le processeur d'accès aux données: PAC</u>             | 131 |

| A - Introduction                                                       | 132 |

| B - Synchronisation entre PAC et FILE                                  | 132 |

| C - Chemin de données du processeur PAC                                | 134 |

| I - Rappel sur les modes d'adressage                                   | 134 |

| II - Décodage des noms d'une variable                                  | 136 |

| D - Gestion de la mémoire associative                                  | 137 |

| I - Format des informations                                            | 137 |

| II - Description de la mémoire associative                             | 137 |

| III - Opérations sur la mémoire associative                            | 139 |

| E - Construction des littéraux                                         | 142 |

| F - Les instructions d'appel et de retour des procédures               | 146 |

| I - L'instruction CALL                                                 | 146 |

| II - L'instruction ENTER                                               | 151 |

| III - L'instruction RETURN                                             | 155 |

| IV - L'appel et le retour des procédures externes                      | 156 |

|                                                                            |         |

|----------------------------------------------------------------------------|---------|

| G - Structure du microprogramme du processeur PAC                          | 158     |

| I - Décodage des instructions d'accès                                      | 158     |

| II - Séquence d'accès à l'instruction suivante                             | 160     |

| III - Interprétation des instructions d'accès                              | 161     |

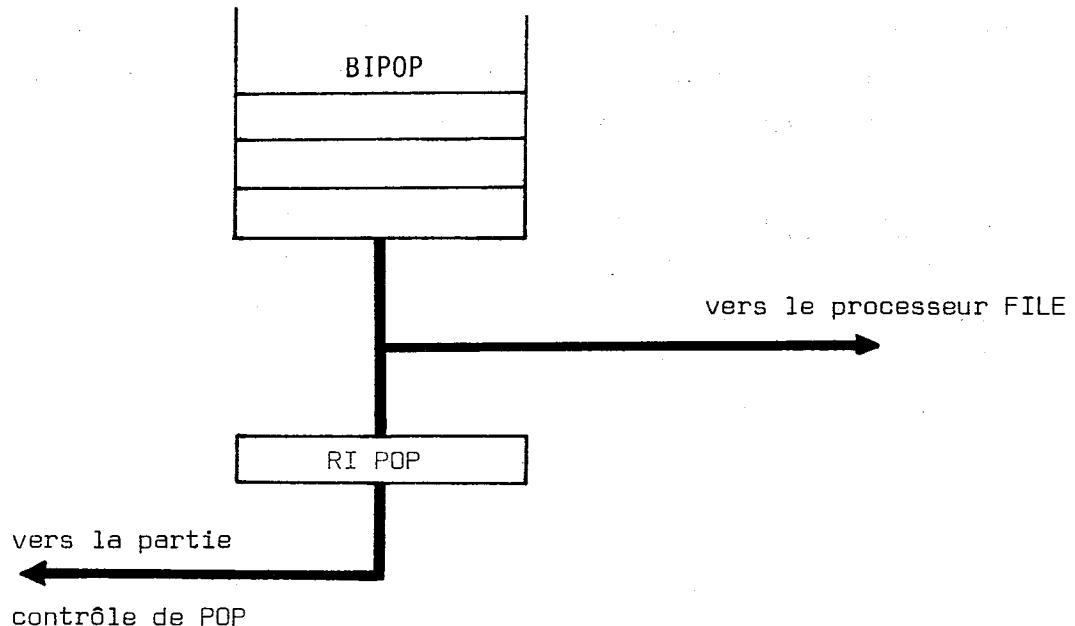

| <br><u>CHAPITRE 5 - Le processeur opératif POP</u>                         | <br>163 |

| A - Introduction                                                           | 164     |

| B - Synchronisation entre POP et FILE                                      | 166     |

| C - Exécution des opérations de contrôle                                   | 168     |

| D - Préparation des opérations arithmétiques                               | 170     |

| E - Exécution des opérateurs                                               | 174     |

| I - Opérateur INDEX                                                        | 174     |

| II - Opérateur CHAMP                                                       | 177     |

| III - Les opérateurs d'allocation dynamique                                | 181     |

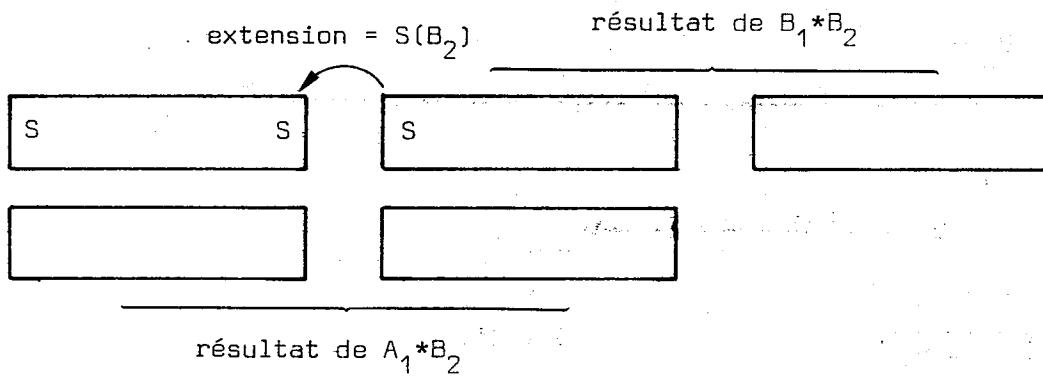

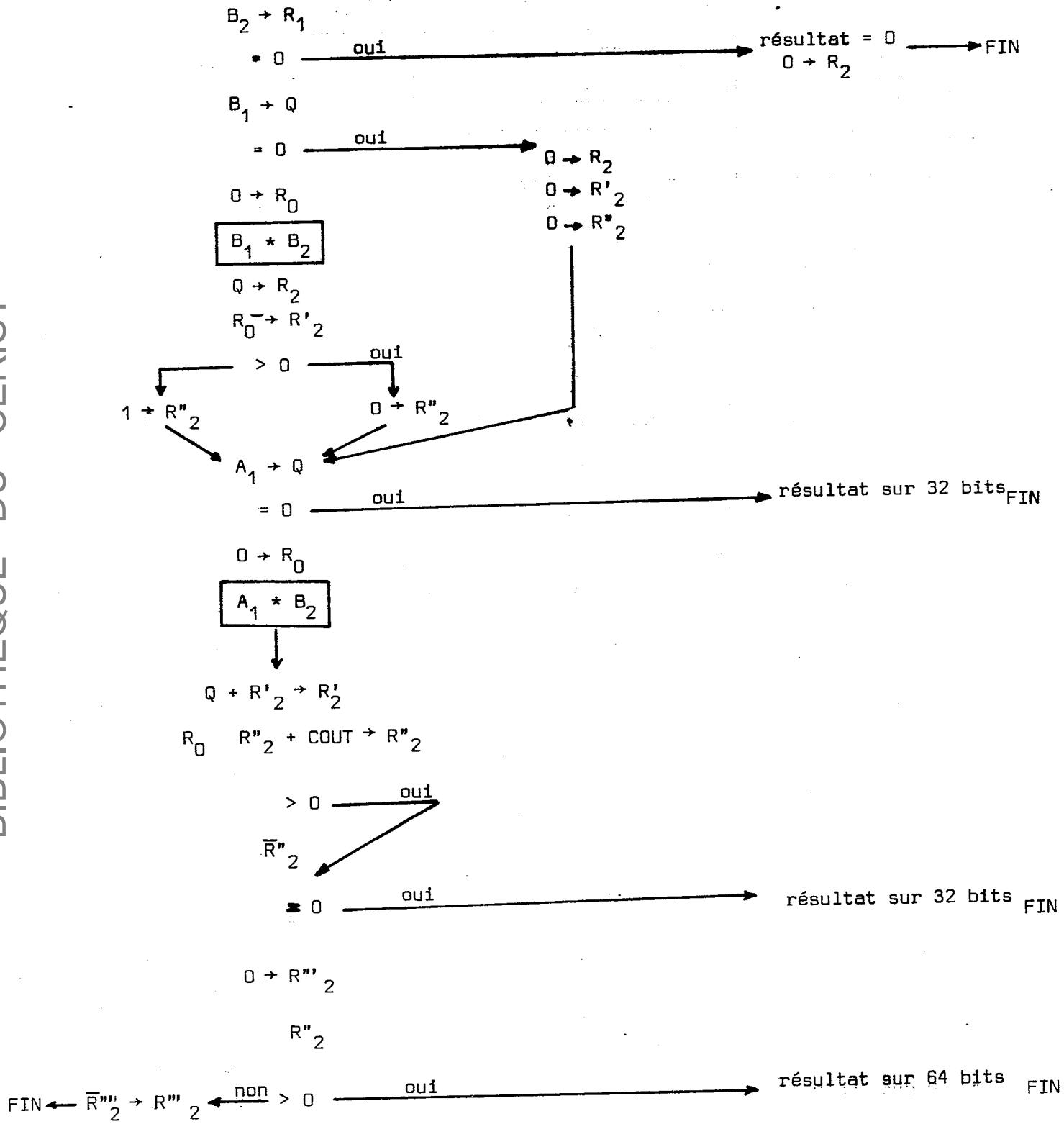

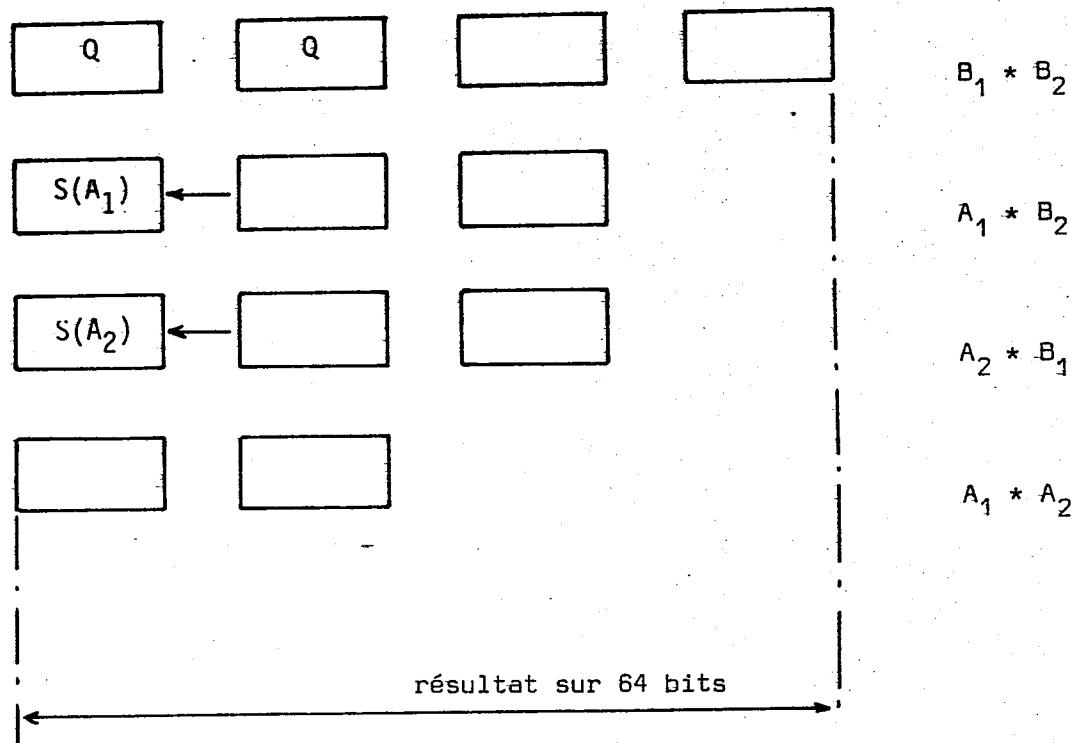

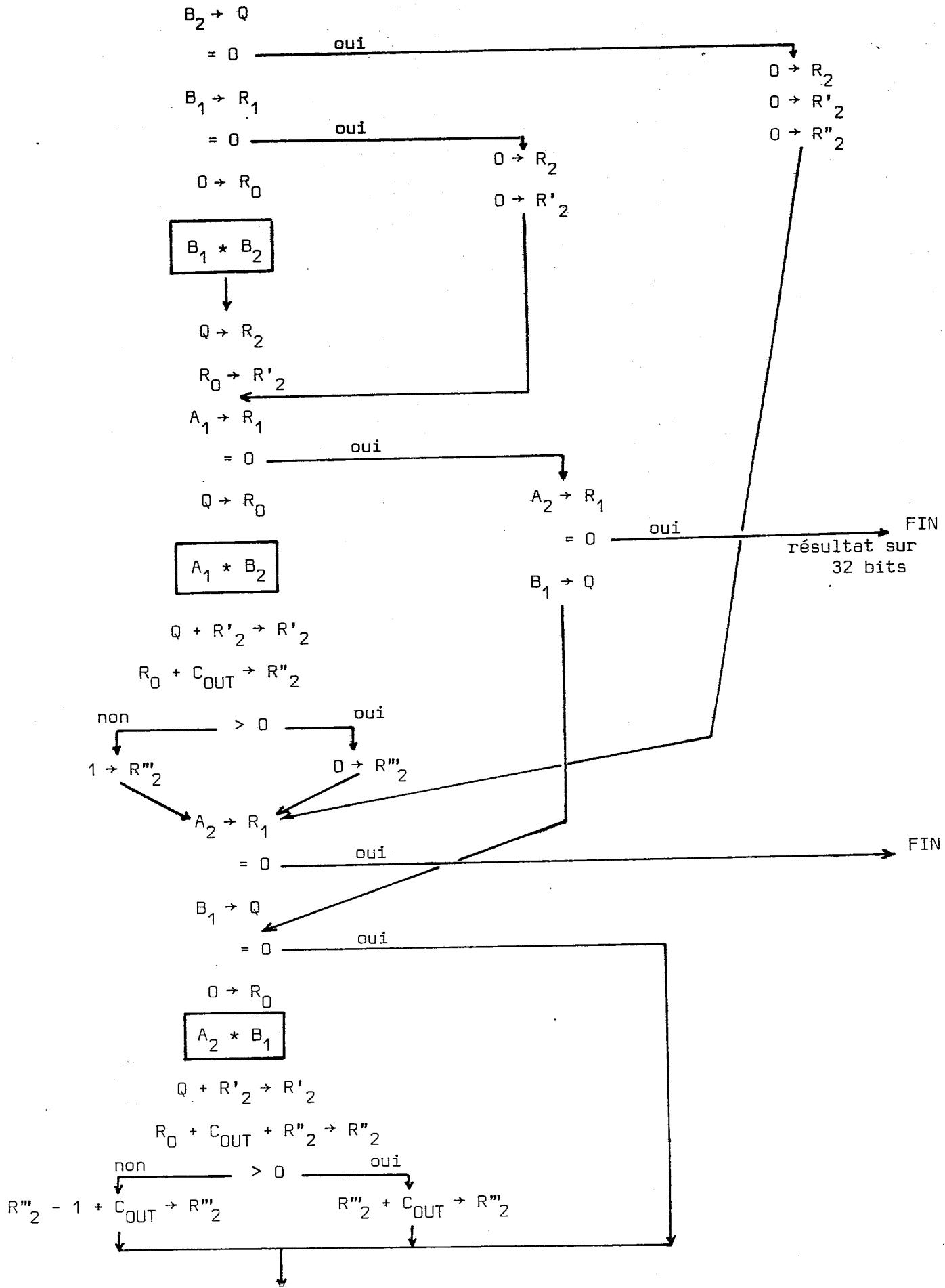

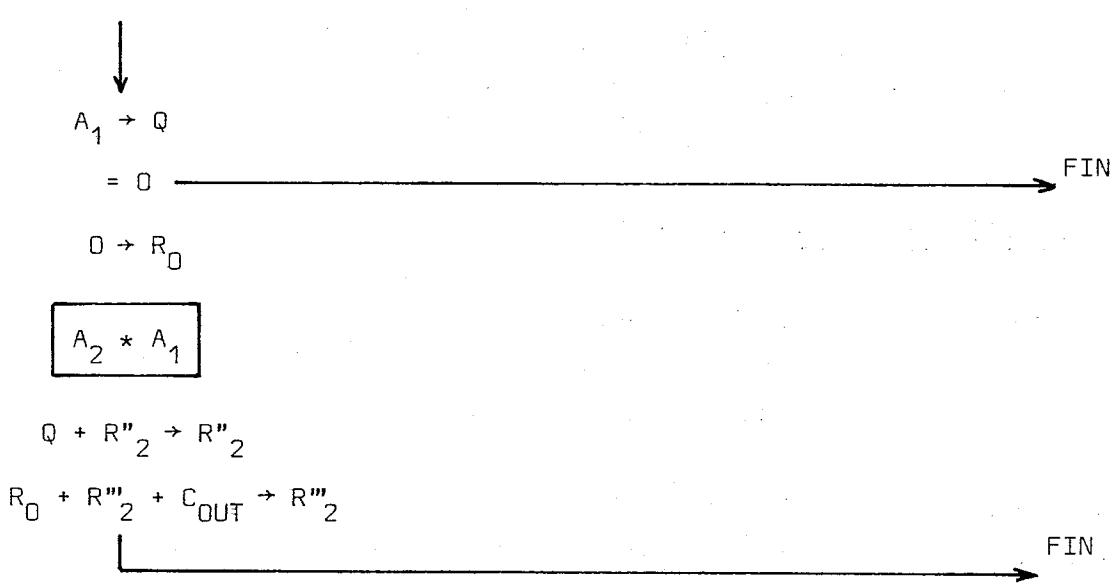

| IV - Réalisation de la multiplication                                      | 185     |

| V - Algorithmes de division entière                                        | 197     |

| VI - Les opérateurs ensemblistes                                           | 202     |

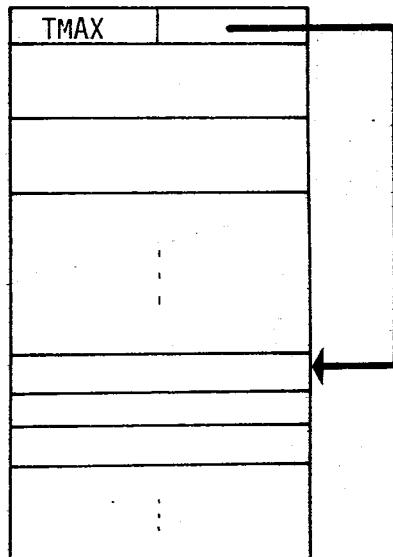

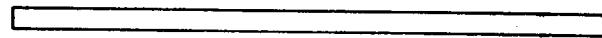

| <br><u>CHAPITRE 6 - Les processeurs de gestion de file</u>                 | <br>204 |

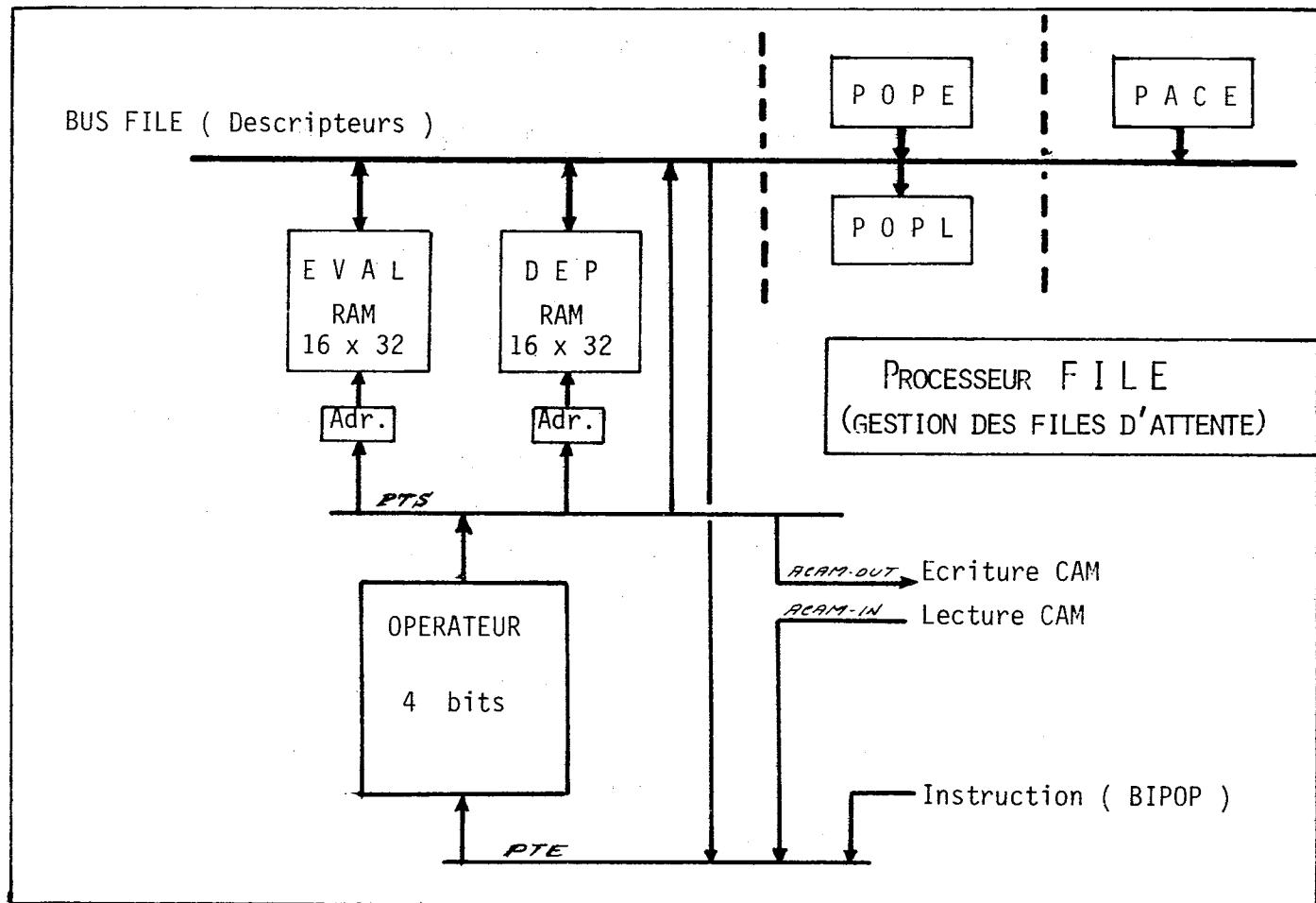

| A - Introduction                                                           | 205     |

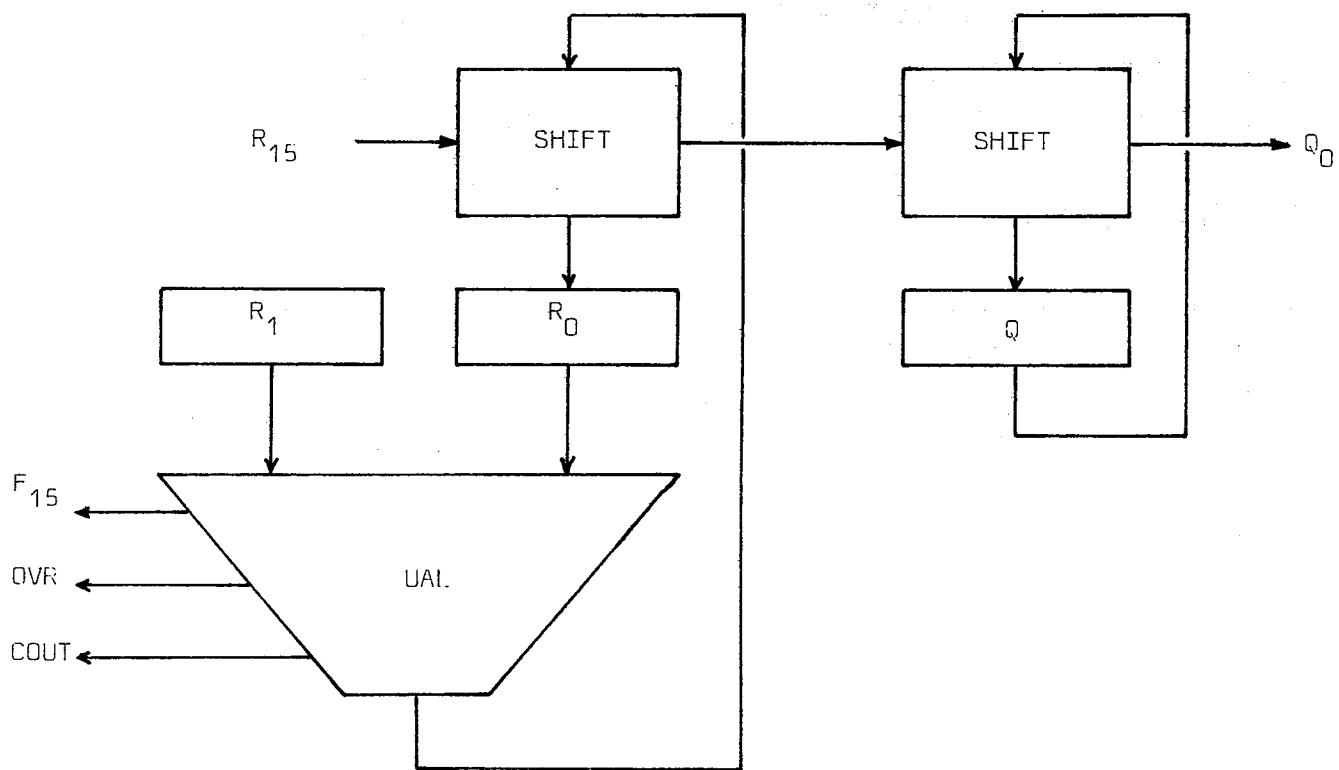

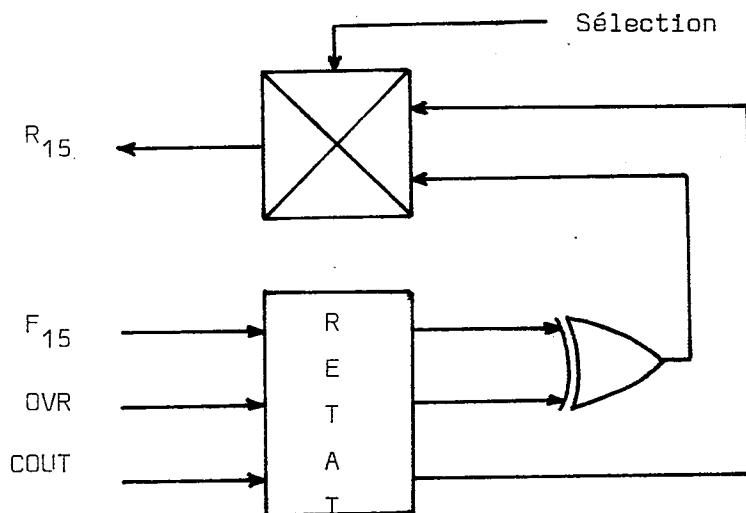

| B - Structure du chemin de donnée du processeur FILE                       | 208     |

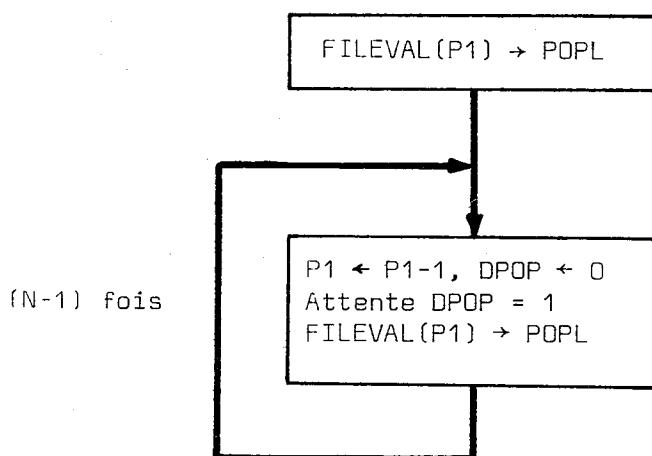

| C - Structure générale du microprogramme                                   | 210     |

| <br><u>CHAPITRE 7 - Le processeur de dialogue avec la mémoire centrale</u> | <br>218 |

| A - Le chemin de données                                                   | 219     |

| B - La fonction d'allocation                                               | 221     |

| <br><u>CONCLUSION</u>                                                      | <br>223 |

| <br><u>ANNEXES</u>                                                         |         |

| - Méthodologie de conception descendante                                   |         |

| Présentation générale                                                      | 227     |

| - Méthode descendante - Application au langage des phases                  | 272     |

BIBLIOTHEQUE DU CERIST

## AVANT-PROPOS

Ce projet de recherche a pris corps au fil des ans, commençant par un D.E.A. en octobre 1972\*. Il se concrétise aujourd'hui.

Il lui manquait cependant un nom qui le caractérise sans ambiguïté et porte en lui-même une certaine sémantique, sans toutefois faire de tort à l'honorable Blaise PASCAL (peut-être est-il mécontent de l'utilisation qui est faite de son nom par les informaticiens).

Nous avons donc fait appel à la langue anglaise pour décrire notre projet comme étant

"a Pipelined Architecture bit Slice Computer for High Level Language"

ce qui donne miraculeusement PASC-HLL, rappelant le langage PASCAL et introduisant le symbole HLL qui met en évidence l'aspect machine-langage de haut niveau.

Ainsi, nous avons le sentiment d'être en règle avec Blaise PASCAL, même si cela pose des problèmes de prononciation à nos contemporains (il existe bien d'autres mnémoniques dans le langage des informaticiens, oh combien moins poétiques et bien souvent dépourvus de sémantique).

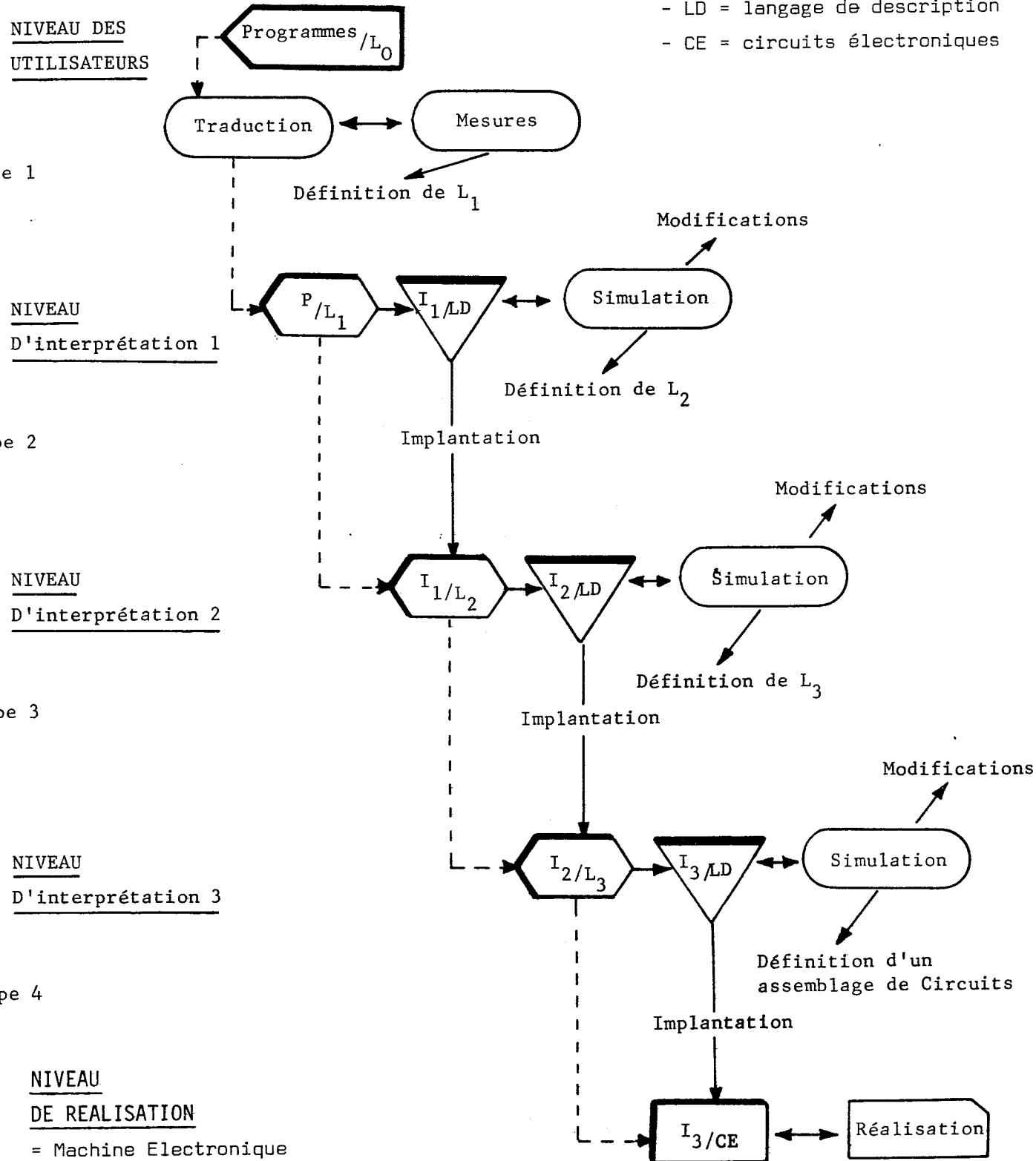

Il est également nécessaire de préciser dans quel contexte cette présentation se situe. C'est le deuxième volet d'une série de trois thèses présentant trois aspects distincts d'un vaste projet: la thèse de R. FORTIER (Octobre 1974 [1]) a montré une approche de définition d'un langage et d'une architecture pour une machine adaptée au langage PASCAL, la seconde (celle-ci) concrétise cette approche par la description d'une architecture pipeline dont la réalisation (en cours) sera décrite dans la future thèse de G. BAILLE, en préparation pour la fin de l'année 1977.

Cette étude est donc le fruit d'un travail d'équipe, qui se concrétise aujourd'hui par la réalisation physique, dans une Université française, d'un ordinateur de grande puissance: ce projet ambitieux, soutenu financièrement par l'IRIA et le

\*Sur une idée de C.OTRAGE.

CNRS (7ème Plan), a pu se poursuivre grâce à la ténacité de son responsable scientifique\* dans le cadre offert par l'Equipe de Recherche en Architecture d'ordinateurs de l'ENSIMAG, qui nous a toujours encouragé de son soutien et prodigué ses conseils.

En quoi le projet PASC-HLL apporte-t-il des notions nouvelles pour la conception des systèmes d'exploitation? Par sa vocation à exécuter d'une manière performante des programmes manipulant des données, elle introduit clairement la notion de processeur de traitement par opposition à un processeur de gestion d'un système d'exploitation. Dans un système classique, ces deux processeurs sont multiplexés sur un seul processeur physique, qui exécute alternativement des programmes de traitement et des programmes de gestion du système d'exploitation, évidemment écrits dans le même langage machine. Un processeur peut-il être adapté à ces deux fonctions à la fois? On nous répondra que l'on peut réaliser n'importe quelle fonction avec un ordinateur mais au prix de quel volume de programmes! Leur taille ne reflète-t-elle pas l'inaptitude du langage-machine à exprimer les fonctions à réaliser?

Quelques études visent à améliorer le fonctionnement global des systèmes, en multipliant par exemple le nombre des Unités Centrales. Ne vaudrait-il pas mieux remettre en cause la nature des Unités Centrales, pour les adapter à la fonction que l'on attend d'elles, plutôt que d'en connecter plusieurs, en se créant artificiellement des problèmes de voisinage? Cette étude propose une approche radicalement opposée et espère susciter des réflexions sur ce thème de recherche.

Nous présentons également un langage-machine, dont l'étude a été abordée dans la thèse FORTIER [1]. Ce langage, voisin de celui des machines BURROUGHS [2], est de type post-fixé. Cette notion a cependant été généralisée, en introduisant des opérations de contrôle du programme, et des opérateurs spéciaux de manipulation de données. Sa définition est issue du langage-source (PASCAL) et de mesures qui ont été réalisées sur des programmes-type. Les travaux de GREBERT [5] et de WORTMAN [6] ont joué un rôle d'initiateur en donnant des recettes intéressantes. Nous avons appliqué ces recettes, en les développant, et nous avons surtout pris

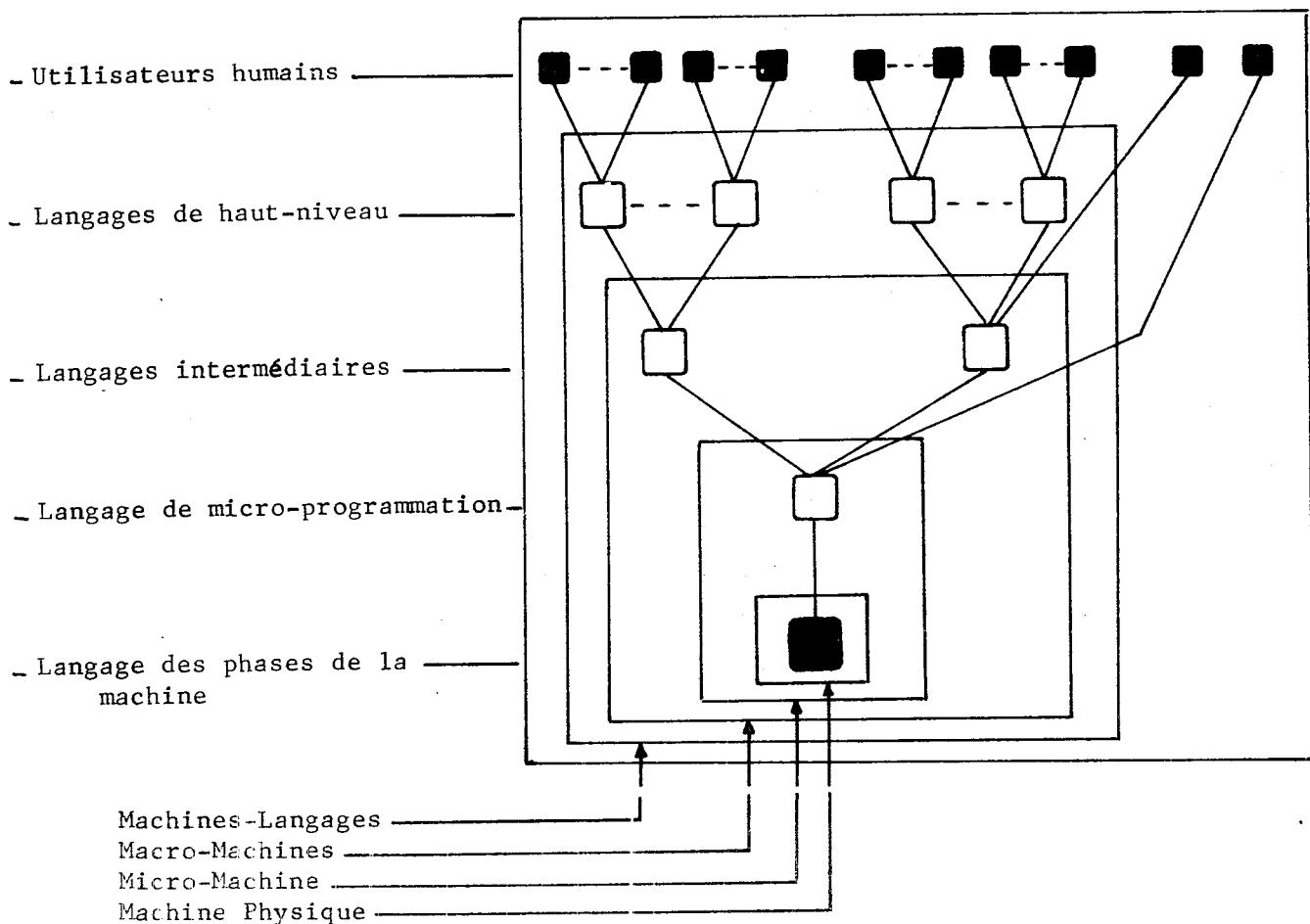

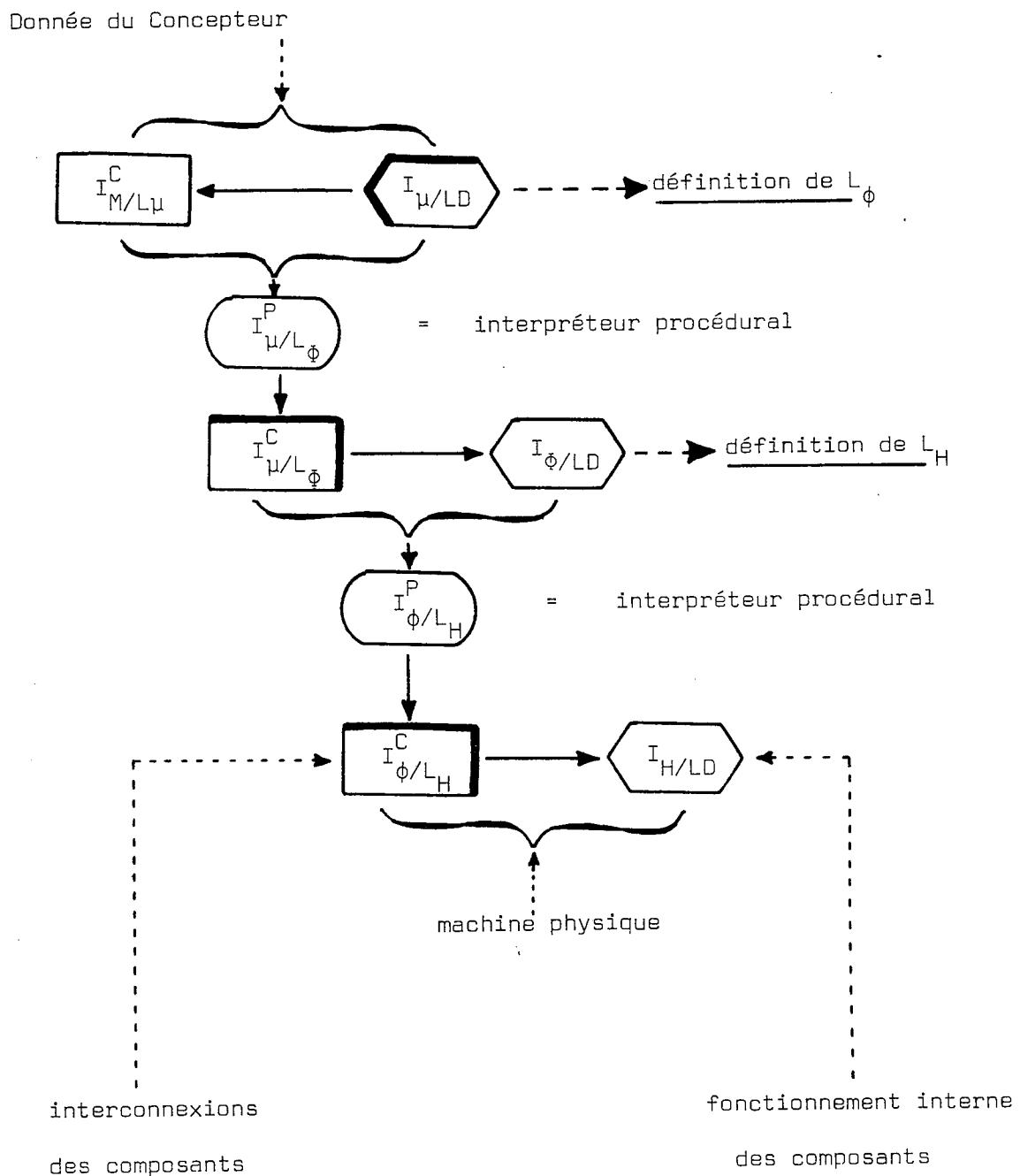

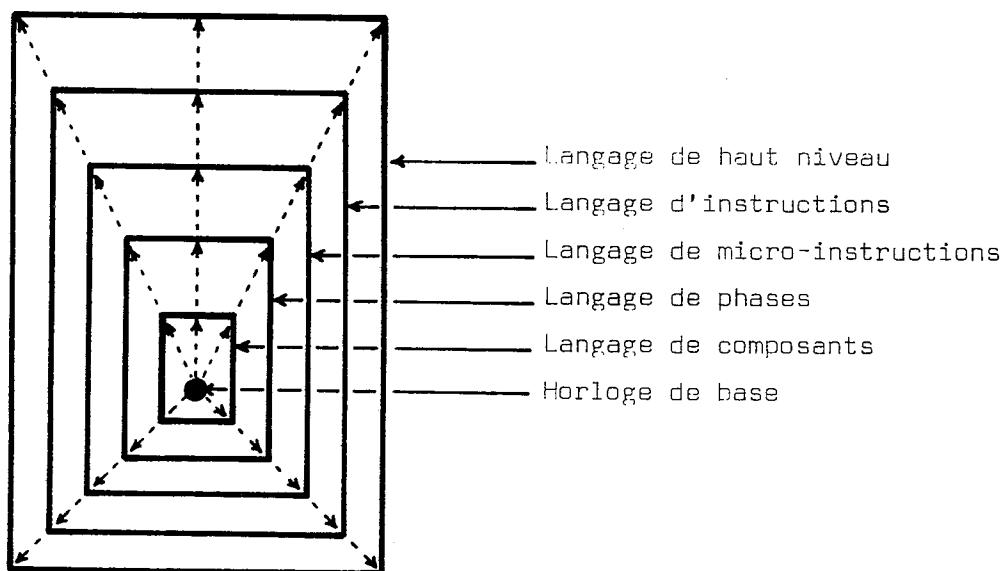

\*François ANCEAU

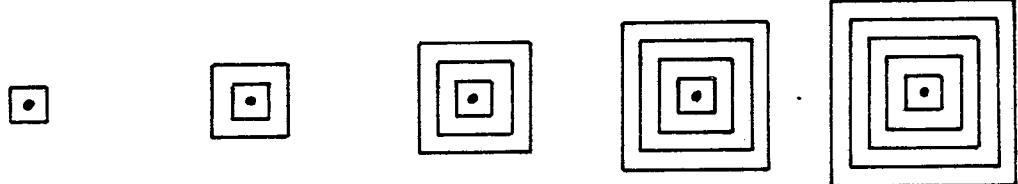

conscience des liens étroits qui existent entre un langage et son interpréteur: rien ne sert de définir un "beau" langage machine, très proche du langage de haut niveau, si son interprétation est problématique ou doit être programmée. Nous pensons en effet pouvoir affirmer que la définition d'un langage, quel que soit son "niveau" dans la hiérarchie des langages doit tenir compte des deux couches entre lesquelles il se situe: la couche supérieure qui est celle de l'utilisation de ce langage pour écrire des programmes, et la couche inférieure qui est l'interpréteur des instructions qui constituent ces programmes. Comme plusieurs couches existent forcément dans tout ordinateur, cette conviction conduit à dire que toutes ces couches doivent toutes être conçues dans une étude unique. A titre de contre-exemple, imaginons que l'étude de PASC-HLL se soit arrêtée à la définition du langage-machine, pour des raisons de crédits ou pour d'autres raisons fort courantes comme la peur de remettre en cause le style de langage des ordinateurs. Il aurait alors pu être envisagé (ou imposé) d'étudier l'interprétation de langage PASC-HLL par un miniordinateur par exemple. Notre étude aurait alors perdu la plus grande partie de son intérêt, et nous aurions peut-être même pu montrer qu'il aurait mieux valu étudier la compilation de PASCAL pour le langage de ce miniordinateur, plutôt que de microprogrammer un interpréteur avec un langage de microprogrammation inadapté.

Notre étude ayant pu, et nous en remercions tous ceux qui l'ont soutenue, dépasser le stade de la "machine-papier-simulée-par-microprogrammation-sur-une-machine-de-base", nous avons abordé la phase de conception d'une architecture spécialisée, sans perdre de vue la définition du langage qui a été très souvent remise en cause, et en tenant compte de la réalisation future et sous-jacente des processeurs qui voyaient le jour dans notre esprit.

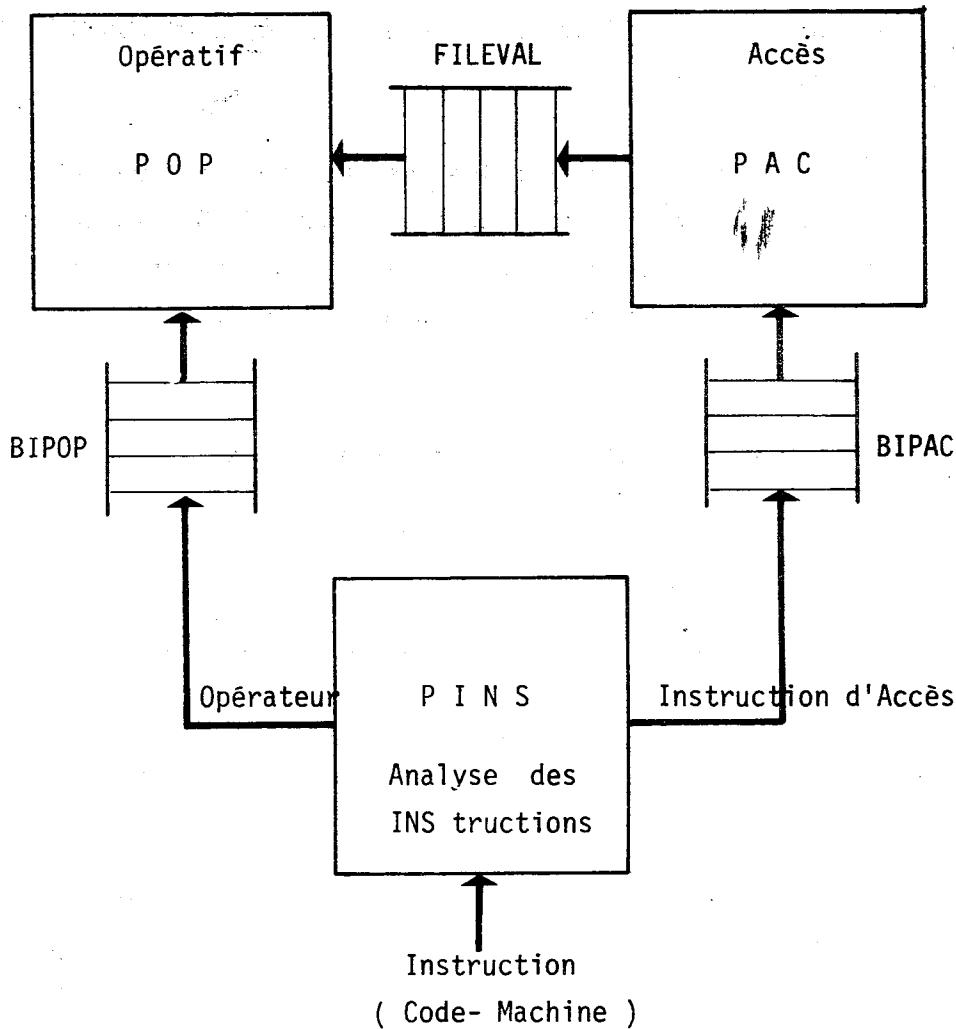

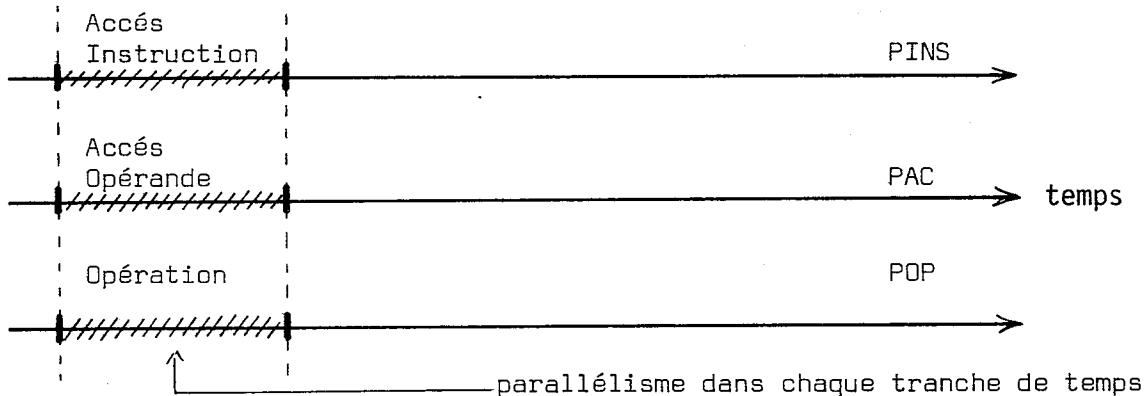

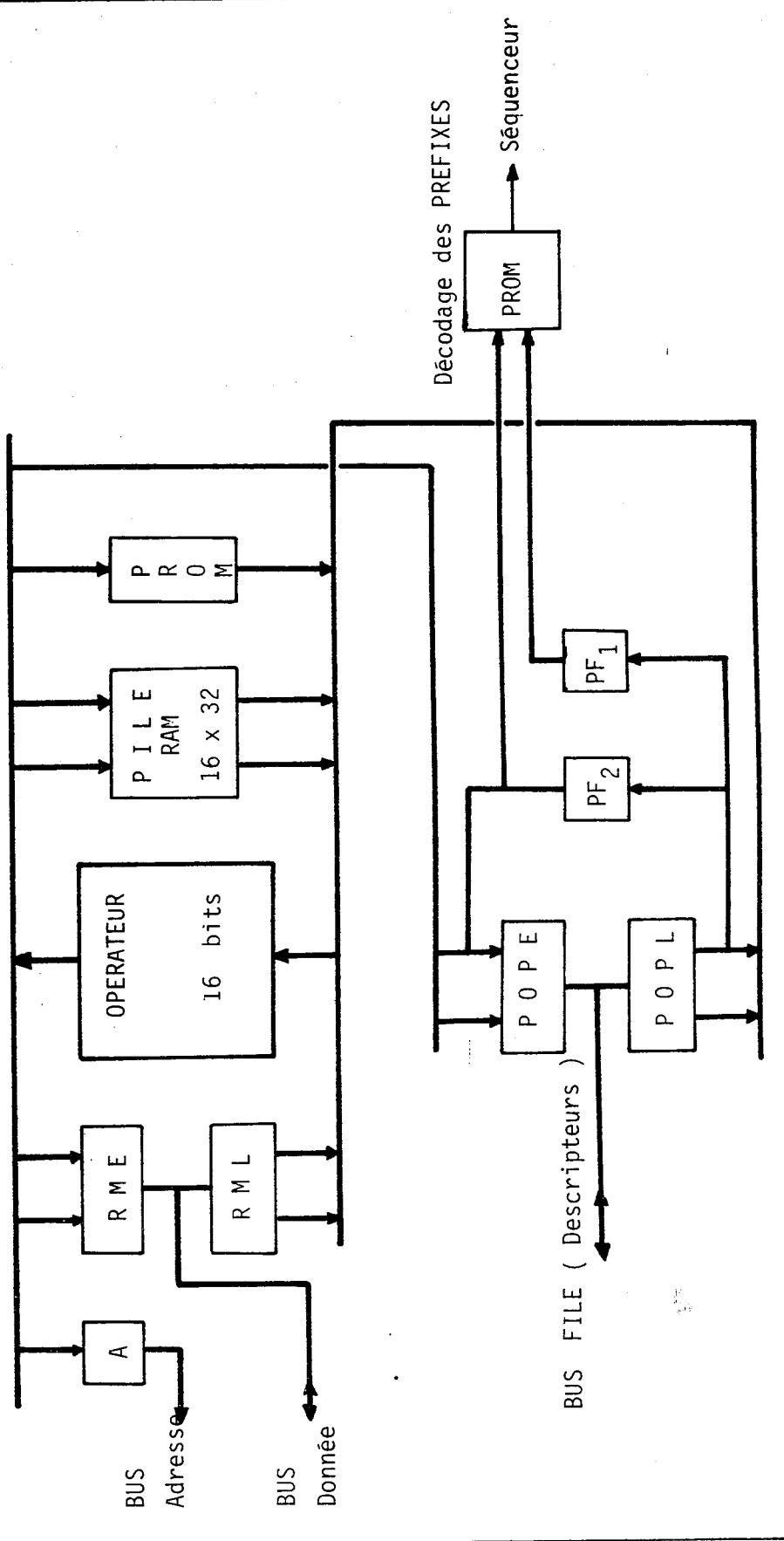

L'idée originale de l'architecture proposée découle d'une décomposition naturelle du fonctionnement d'une Unité Centrale: elle accède à des instructions, elle accède à des données, elle exécute des opérateurs. Il suffisait donc de trouver un mécanisme, si possible simple, qui permette de confier à trois processeurs spécialisés l'exécution de ces trois fonctions qui apparaissent naturellement.

Le gain théorique de performance est évident. Le gain réel est encore inconnu et nous expliquerons pourquoi. Il semblait cependant intéressant d'étudier complètement les possibilités d'une telle décomposition, qui n'est pas déraisonnable si l'on en juge à l'utilisation qui en est faite dans quelques Unités Centrales très puissantes déjà commercialisées (IBM 3033).

De plus, cette architecture met encore en évidence la notion de processeurs fonctionnels qui conduit à la réalisation de machines de petite taille, ultra-spécialisées dans la fonction qu'on leur demande de réaliser. Elle permet d'autre part d'appliquer les méthodes de conception descendante pour la définition de chacun des processeurs.

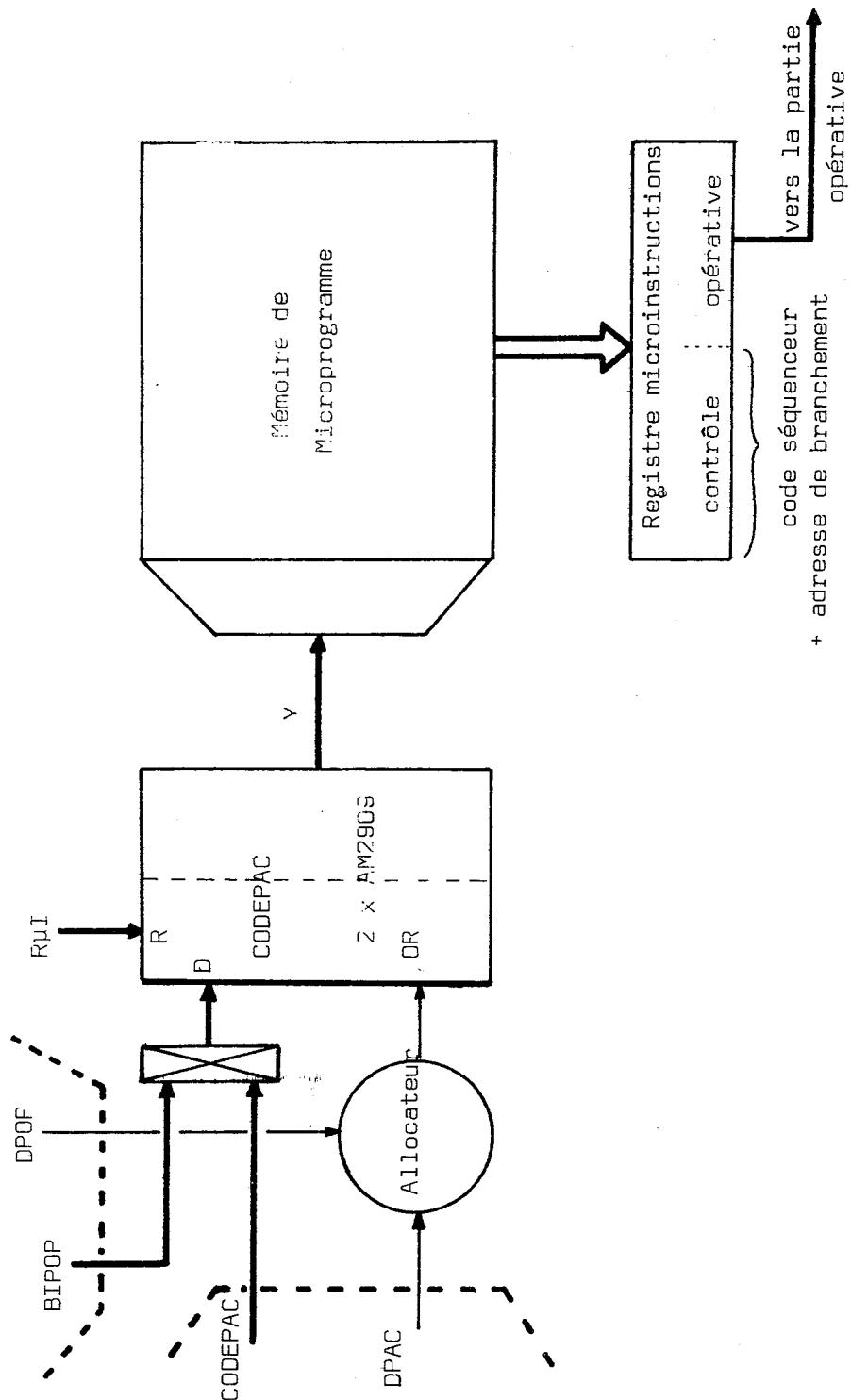

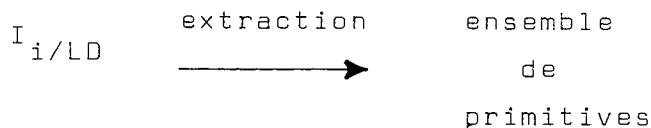

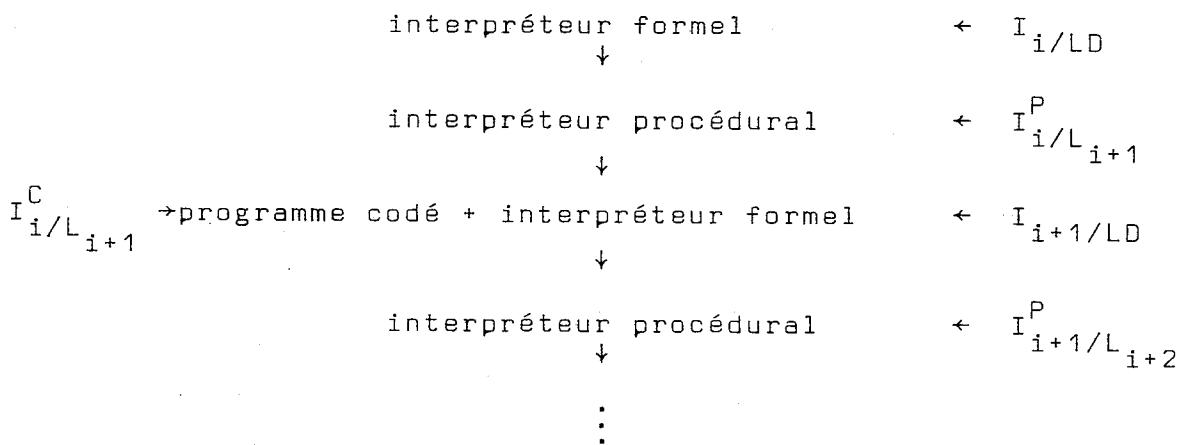

Malgré leur petite taille due à leur spécialisation, les processeurs de PASC-HLL sont chacun une véritable Unité Centrale qui interprète un langage spécialisé. Leur réalisation n'aurait pu être envisagée sans l'apparition providentielle des "macrocomposants" appelés à tort "microprocesseurs en tranches" [7]. En effet, ces composants électroniques regroupent dans un seul boîtier plusieurs composants classiques (MSI) et permettent de construire aisément des structures microprogrammées: la démarche descendante suggère la définition d'un langage de microprogrammation spécialisé en fonction de l'écriture du programme d'interprétation du langage-machine. Cette définition a été faite pour chacun des processeurs en tenant compte du choix des macrocomposants: ils introduisent une notion de cycle, correspondant à l'exécution d'une microinstruction. Il suffit donc de connaître ce qui est "exécutable en un cycle" pour définir le langage de microprogrammation.

La réalisation électronique représente l'étape suivante de la démarche: elle sera présentée en détail dans la troisième thèse (G.BAILLE, fin 1977)[8].

- La première partie de ce document présente les aspects généraux de PASC-HLL: les "aspects système d'exploitation", après avoir situé PASC-HLL dans l'environnement d'un système d'exploitation, décrivent l'organisation des données manipulées par la machine (son espace d'adressage) et les problèmes d'entrée/sortie qui illustrent la répartition du traitement des éléments de fichiers par un

compromis entre la programmation de certaines procédures et la microprogrammation des fonctions de conversion entre une représentation externe (alphanumérique) et interne (binaire). Enfin, dans un deuxième chapitre, les principales caractéristiques du langage-machine et l'architecture générale de PASC-HLL sont successivement présentées.

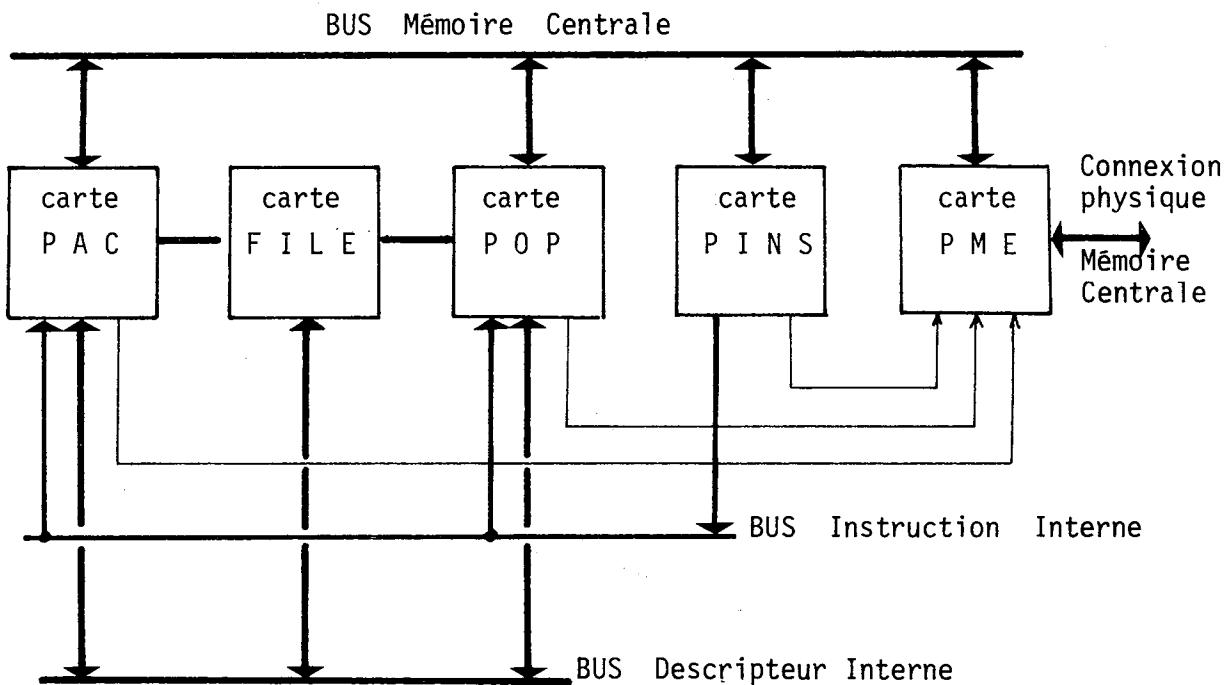

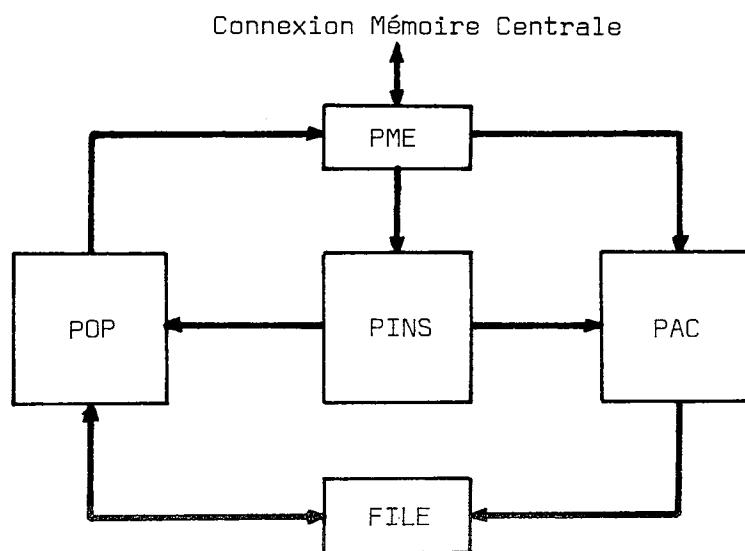

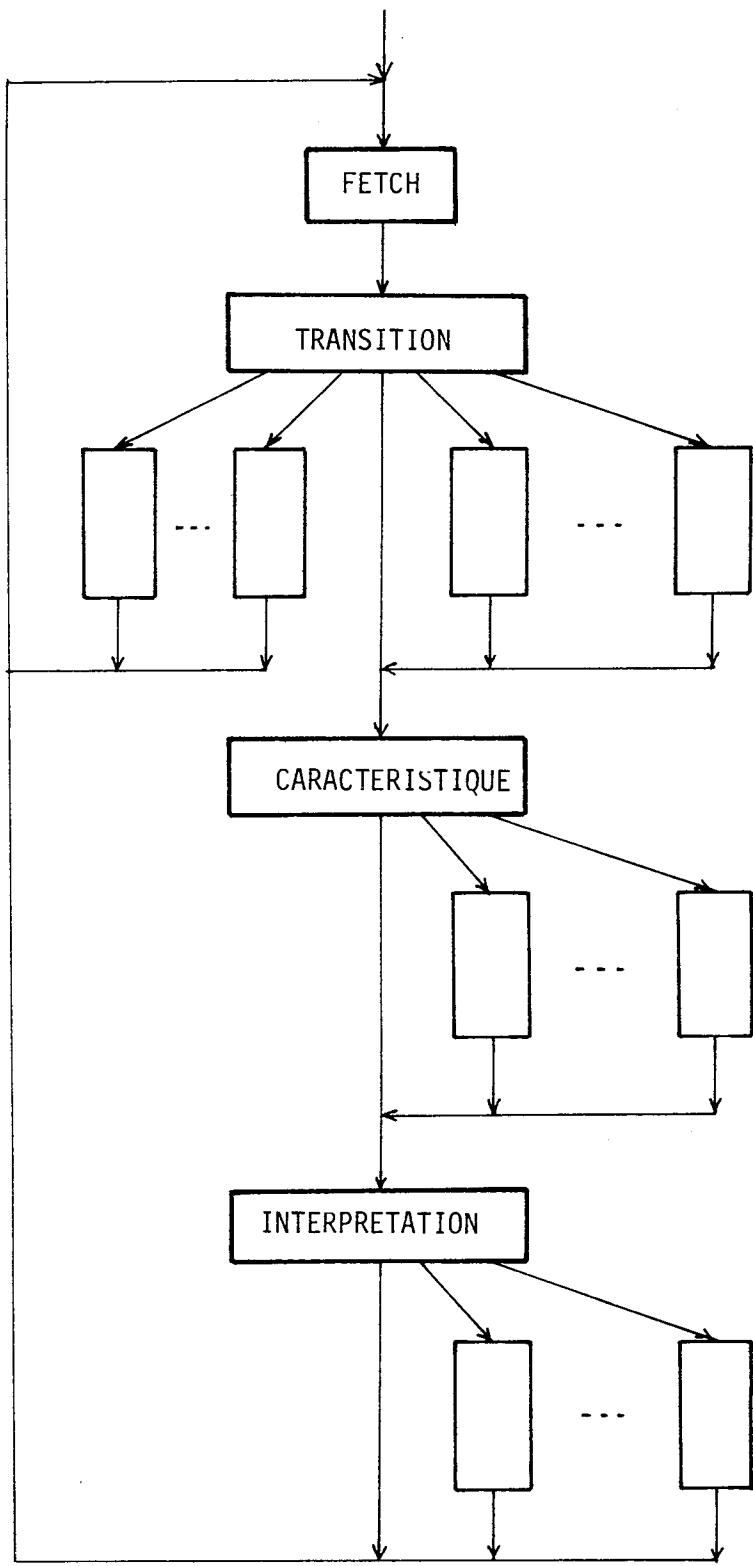

- La deuxième partie décrit successivement les cinq processeurs qui constituent PASC-HLL. Pour chacun d'eux, on situe son rôle dans l'architecture pipeline, on présente les problèmes de synchronisation et l'algorithme général qu'il doit réaliser. Ceci nous conduit à proposer des microprogrammes, écrits d'une manière symbolique, pour décrire les fonctions à réaliser. Ces microprogrammes "formels" seront à leur tour étudiés afin de définir des machines électroniques spécialisées dans leur interprétation (la machine électronique interprète le langage de microprogrammation).

L'ensemble des trois thèses relatives à PASC-HLL couvre ainsi une conception globale d'ordinateur, de l'utilisateur du langage de haut niveau au fonctionnement des composants électroniques. De plus, cette étude théorique se concrétise aujourd'hui par la réalisation physique d'un prototype qui sera, nous l'espérons, en mesure de montrer si les mécanismes proposés présentent l'intérêt que nous leur supposons.

En annexe, un essai de formalisation de la méthode de conception descendante est présenté.

BIBLIOTHEQUE DU CERIST

P R E M I E R E   P A R T I E

---

---

CHAPITRE 1 : LES ASPECTS "SYSTEME" DE "PASC-HLL"

CHAPITRE 2 : PRESENTATION GENERALE DE L'ARCHITECTURE DE "PASC-HLL"

BIBLIOTHEQUE DU CERIST

CHAPITRE 1

A - INTRODUCTION: Insertion de PASC-HLL dans un "système"

B - L'ESPACE D'ADRESSAGE DE LA MACHINE

- I - Structuration de l'espace d'adressage

- II - Adressage des quatre zones de l'espace virtuel

- III - Organisation des zones CODE et EXTERNE

- IV - Organisation de la zone CONTEXTE

- V - Organisation de la zone DYNAMIQUE

C - LES ENTREES/SORTIES

- I - Structure des informations

- II - Exécution des opérations d'entrée/sortie

- III - Les entrées/sorties évoluées

- IV - Conclusion

## A - INTRODUCTION

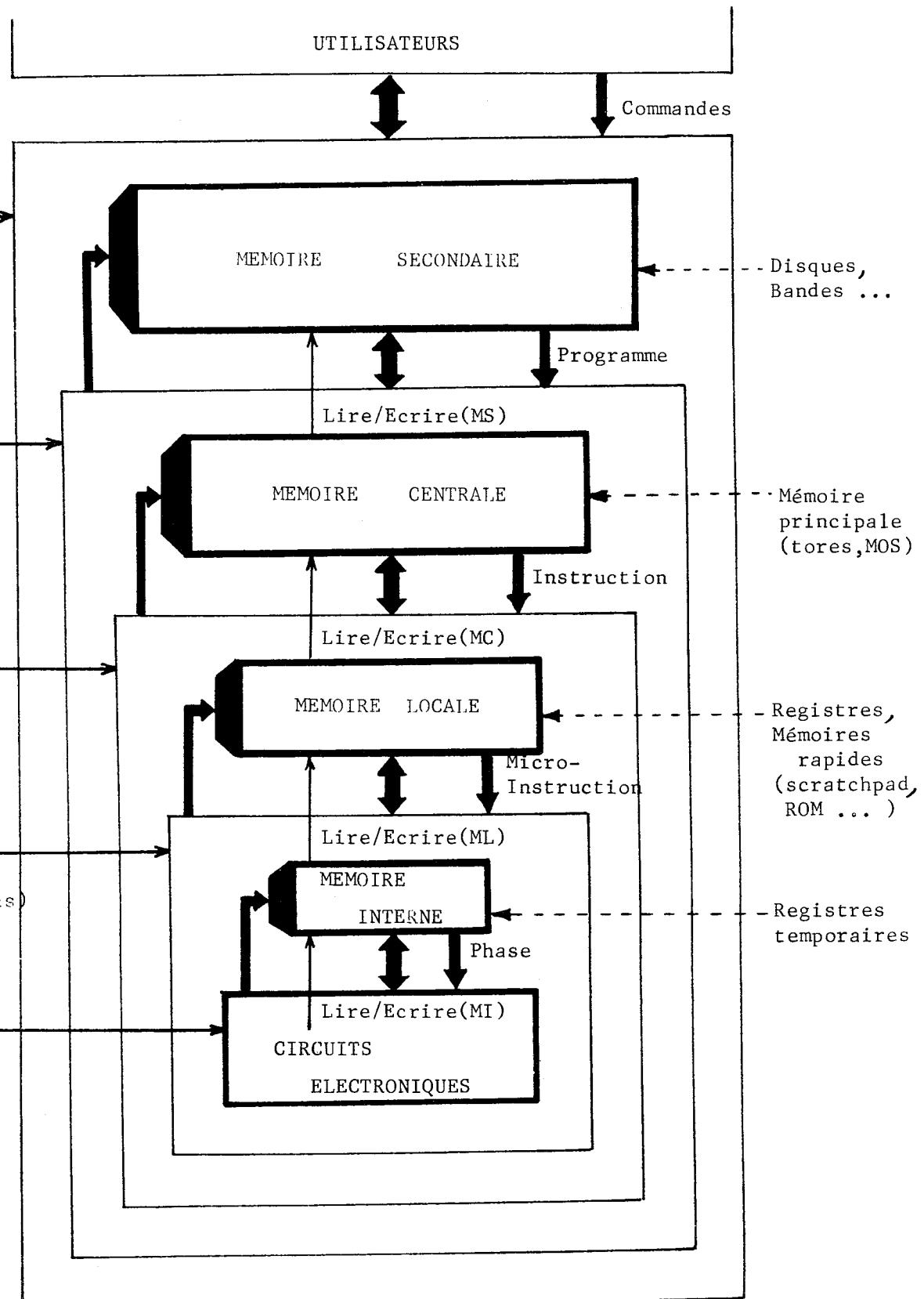

La machine PASC-HLL a été définie comme un processeur de traitement spécialisé dans l'exécution de programmes manipulant des données situées dans une Mémoire Centrale. Cette définition implique qu'elle n'est pas concernée par les opération d'entrée/sortie, au sens du transfert d'informations entre un périphérique et la Mémoire Centrale, ni par la gestion globale des programmes soumis au système d'exploitation par les utilisateurs.

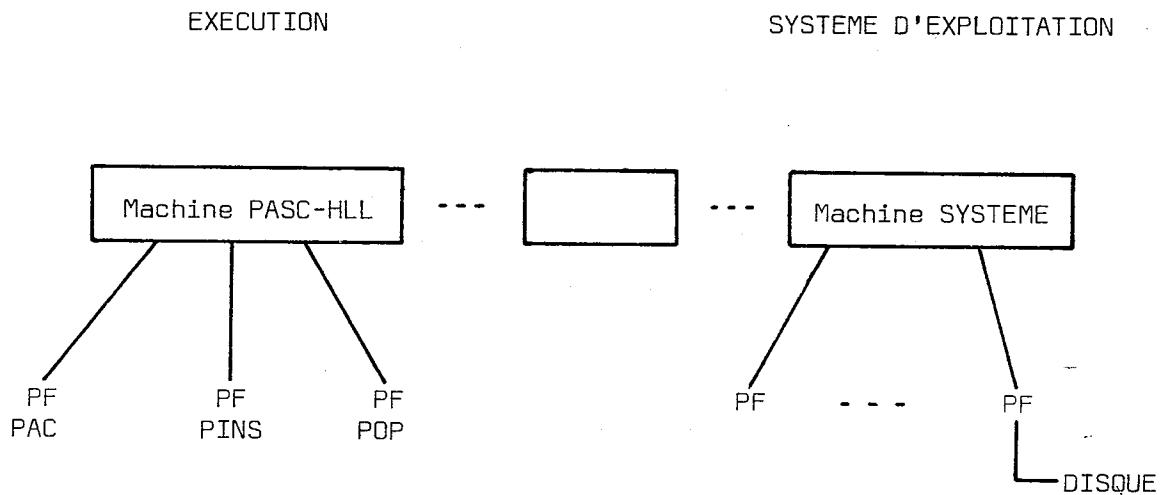

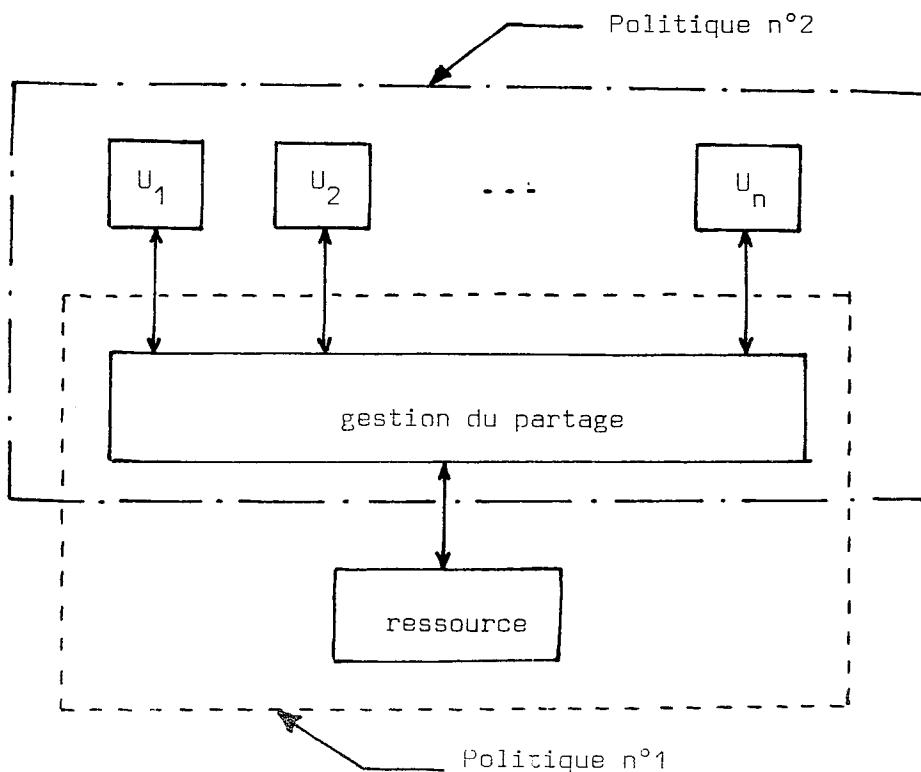

Cette approche illustre la notion de processeurs fonctionnels que l'on retrouve dans[4], qui fait apparaître une répartition des fonctions à réaliser: dans notre cas, PASC-HLL réalise la fonction d'exécution des programmes et les fonctions "système d'exploitation" sont laissées à la charge d'une autre Unité centrale, que nous appellerons la Machine Hôte exécutant le Système Hôte, ou tout simplement Machine-Système.

Cette étude d'un processeur spécialisé dans le traitement fait d'ailleurs apparaître les spécifications d'un processeur spécialisé dans l'exécution d'un système d'exploitation, dont le travail se réduirait :

- à la gestion des programmes dans un système de type "traitement par lot",

- à la gestion de la Mémoire Centrale,

- au dialogue avec les organes d'entrée/sortie (périphériques).

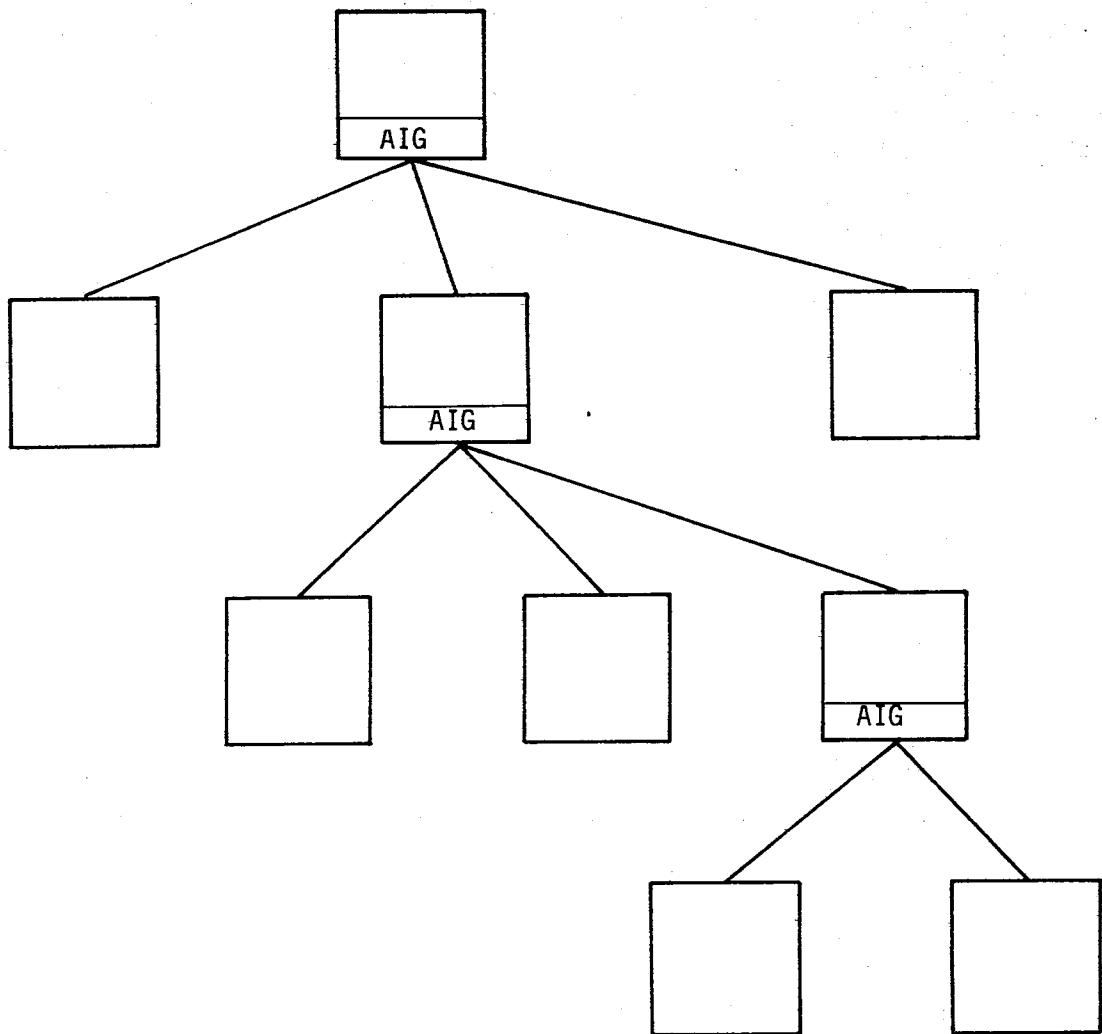

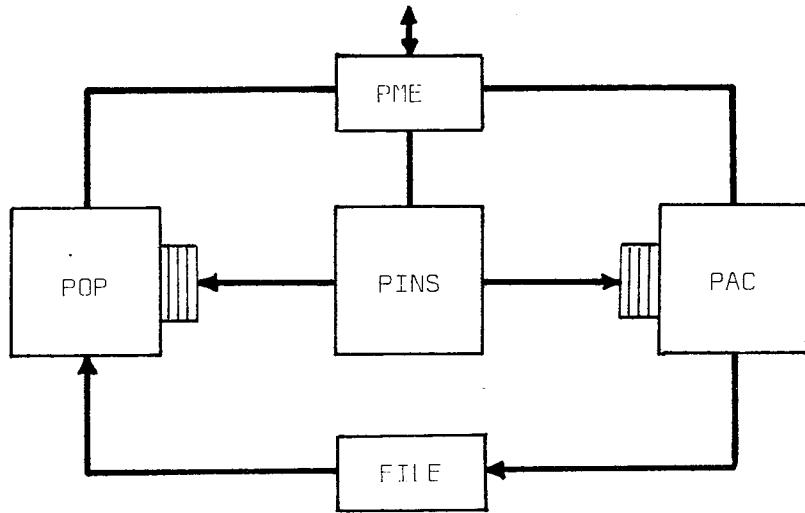

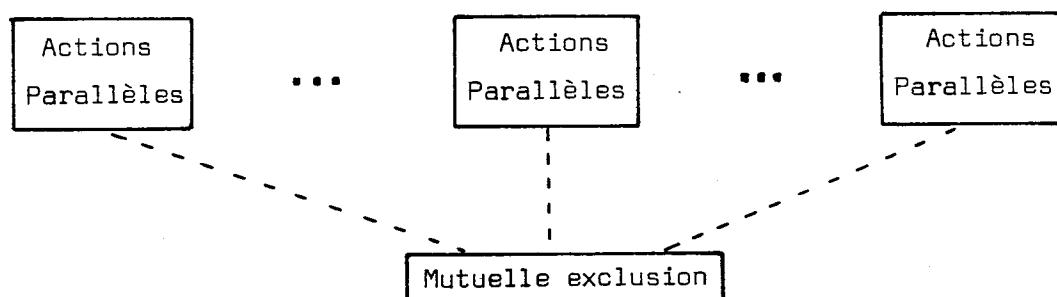

Cette décomposition fonctionnelle ne doit pas être restreinte à deux processeurs (PASC-HLL et la Machine-Système-Hôte), et une approche hiérarchisée de la décomposition doit être envisagée: la machine PASC-HLL elle-même en est un exemple, avec ses trois processeurs fonctionnels de traitement des instructions (PINS), d'accès aux opérandes (PAC) et d'exécution des opérateurs (POP). En ce qui concerne la Machine Système, plusieurs études sont en cours, qui proposent par exemple un processeur de gestion de fichiers [9], et répartissent les fonctions systèmes entre plusieurs processeurs spécialisés [ 3 ].

### I.- MULTIPROGRAMMATION FONCTIONNELLE

La répartition fonctionnelle choisie implique un mode de fonctionnement particulier que nous appellerons multiprogrammation fonctionnelle caractérisée par le fait que plusieurs programmes sont présents dans le système global à un instant donné, l'un requérant la fonction d'exécution (PASC-HLL), l'autre une fonction système exécutée par la Machine Système.

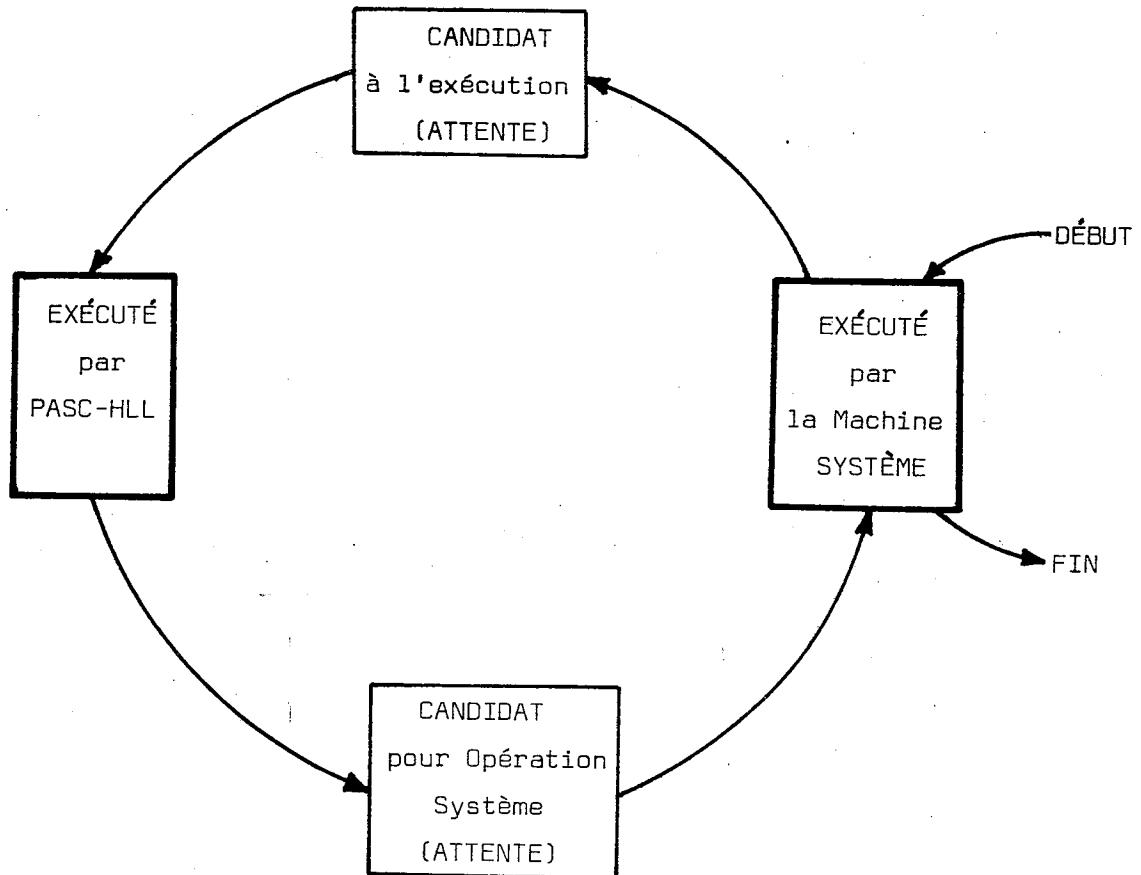

Suivons la vie d'un programme dans le système global:

- Son initialisation est du ressort de la Machine-Système qui réalise les opérations d'Edition de Liens entre les modules et les fichiers. Elle se termine lorsque tout est prêt pour l'exécution. Le programme devient alors "candidat à l'exécution".

- Tout programme "candidat à l'exécution" peut être fourni à la machine PASC-HLL. Cette dernière exécute les instructions qui le composent et arrête cette exécution lorsqu'elle détecte une instruction-système qui n'est pas de sa compétence. Le programme devient alors "candidat pour une Opération-Système".

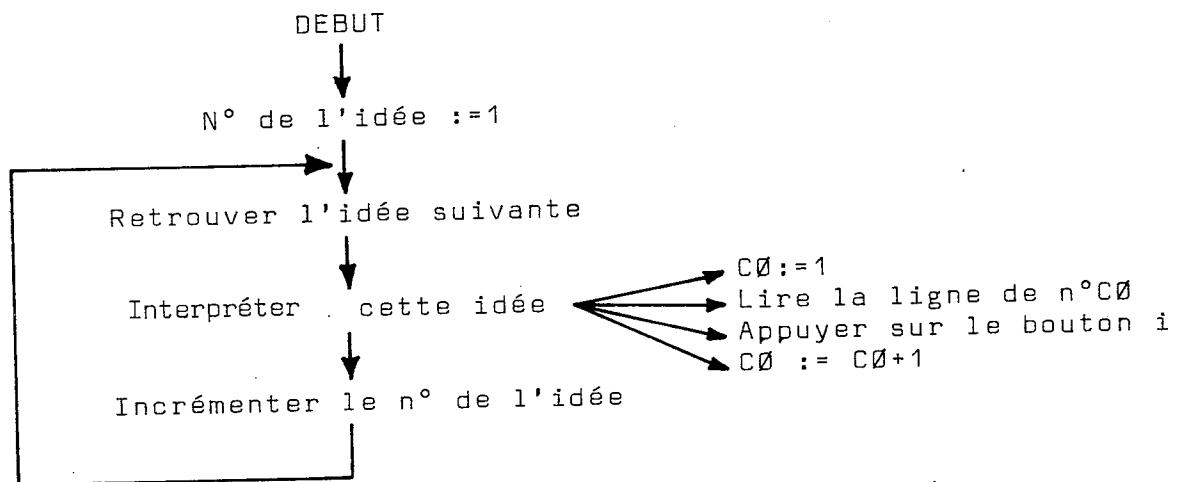

La figure présente les différents états possibles pour un programme.

## II - REALISATION DU PARTAGE DES PROGRAMMES

Le fonctionnement en multiprogrammation fonctionnelle suppose un "transfert" des programmes entre la fonction d'exécution et la fonction "système". La réalisation physique d'un tel transfert serait trop lente et poserait de toutes manières des problèmes de conflits d'accès aux informations situées dans une mémoire partagée.

La solution proposée repose sur l'utilisation d'une Mémoire Centrale unique partagée par les deux processeurs (PASC-HLL et la Machine-Système). Elle suppose, dans les conditions idéales:

- que la Mémoire Centrale soit physiquement composée de plusieurs blocs indépendants,

- que les deux processeurs puissent physiquement accéder à tous les blocs.

Dans ces conditions, toutes les données relatives à l'exécution d'un programme se trouvent dans le même bloc physique. Chaque bloc physique est alternativement accédé par PASC-HLL (lorsqu'il contient le programme en exécution) et par la Machine-Système (lorsqu'il contient un programme pour lequel une opération système est exécutée).

Cette organisation de la Mémoire Centrale suppose de plus l'existence d'un mécanisme de communication entre les deux unités centrales:

- la Machine Centrale doit fournir à PASC-HLL l'adresse (numéro) du descripteur du programme candidat à l'exécution ;

- PASC-HLL doit avertir la Machine-Système que le programme contenu dans le bloc physique qui lui était alloué requiert l'exécution d'une opération système, et demande ainsi l'allocation d'un autre bloc physique contenant le candidat suivant à l'exécution.

Exemple de réalisation:

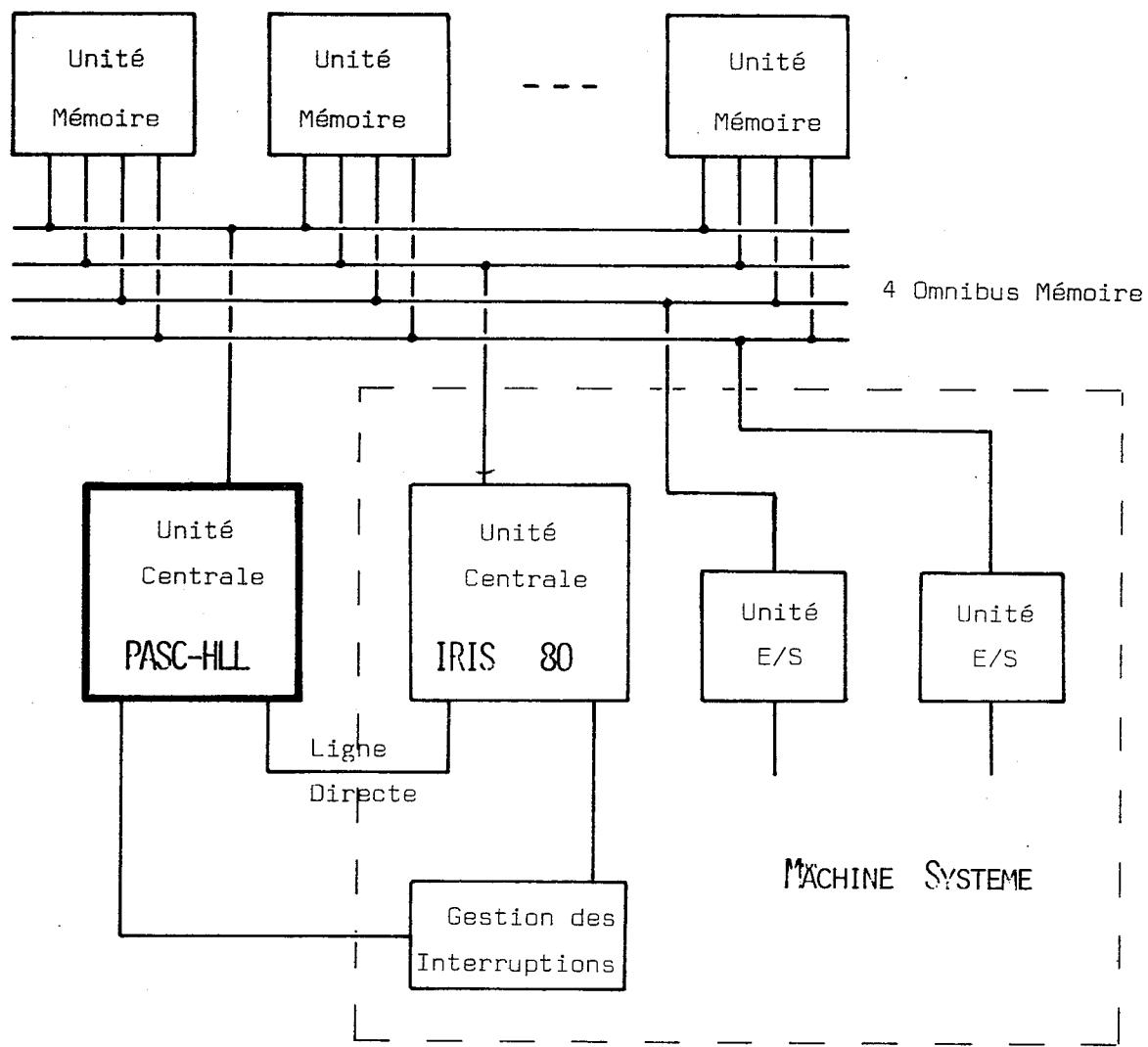

Un tel système est à première vue réalisable à titre d'exemple, sur un ordinateur IRIS 80.

Nous nous limitons ici à donner une approche du problème de connexion à un tel ordinateur, montrant que l'idée est réalisable, et également pour susciter des réflexions sur une nouvelle organisation d'un système classique.

La Mémoire Centrale de l'ordinateur IRIS 80 est composée de 1 à 8 Unités Mémoire (UM) possédant de 2 à 8 voies d'accès (auxquelles sont associés des niveaux de priorité) et constituée chacune de 1 ou 2 blocs, chaque bloc contenant 128 ou 256 K octets.

On peut donc avoir, dans une configuration Mémoire maximum, 16 blocs de 256 K octets autonomes et asynchrones utilisés simultanément par 8 utilisateurs connectés aux 8 voies d'accès possibles.

Une configuration possible pour l'insertion de PASC-HLL dans un système IRIS 80 serait:

La liaison programmée (instruction WD écriture directe) pourrait être utilisée par l'Unité Centrale IRIS 80 pour transmettre à l'Unité Centrale PASC-HLL le numéro du bloc (4 bits) dans lequel se trouve le programme à exécuter. A l'opposé, PASC-HLL émettrait un "Interruption" pour avertir l'Unité Centrale IRIS 80 qu'elle doit abandonner un programme pour cause d'opération-système.

Dans une telle organisation, il n'existe pas de conflit d'accès à un bloc de la Mémoire Centrale, sachant que:

- les liaisons physiques (OMNIBUS) sont indépendantes,

- une seule Unité Centrale accède à un bloc à un instant donné.

Il n'y a donc pas de problème de priorité entre les deux unités centrales.

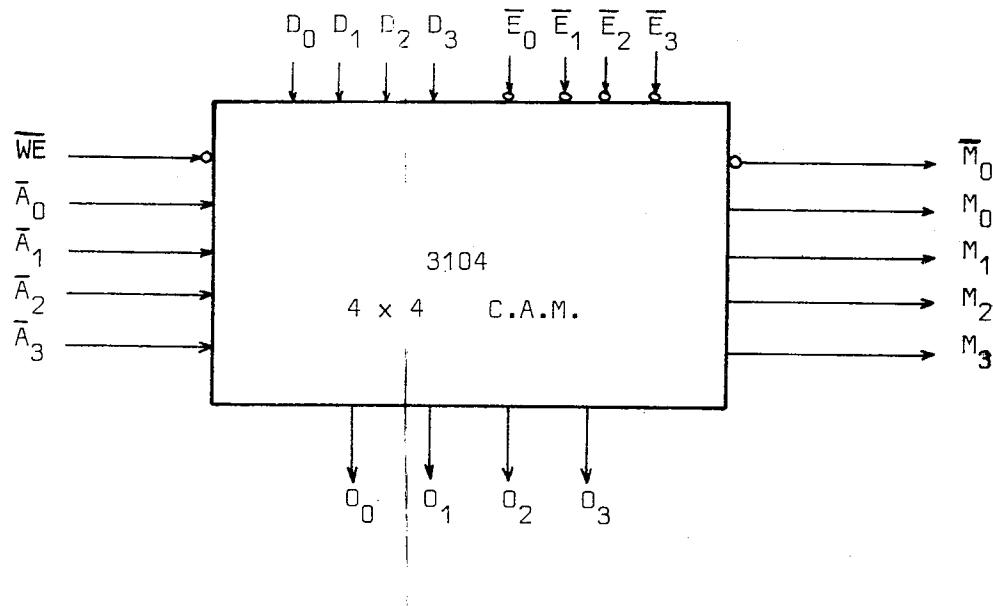

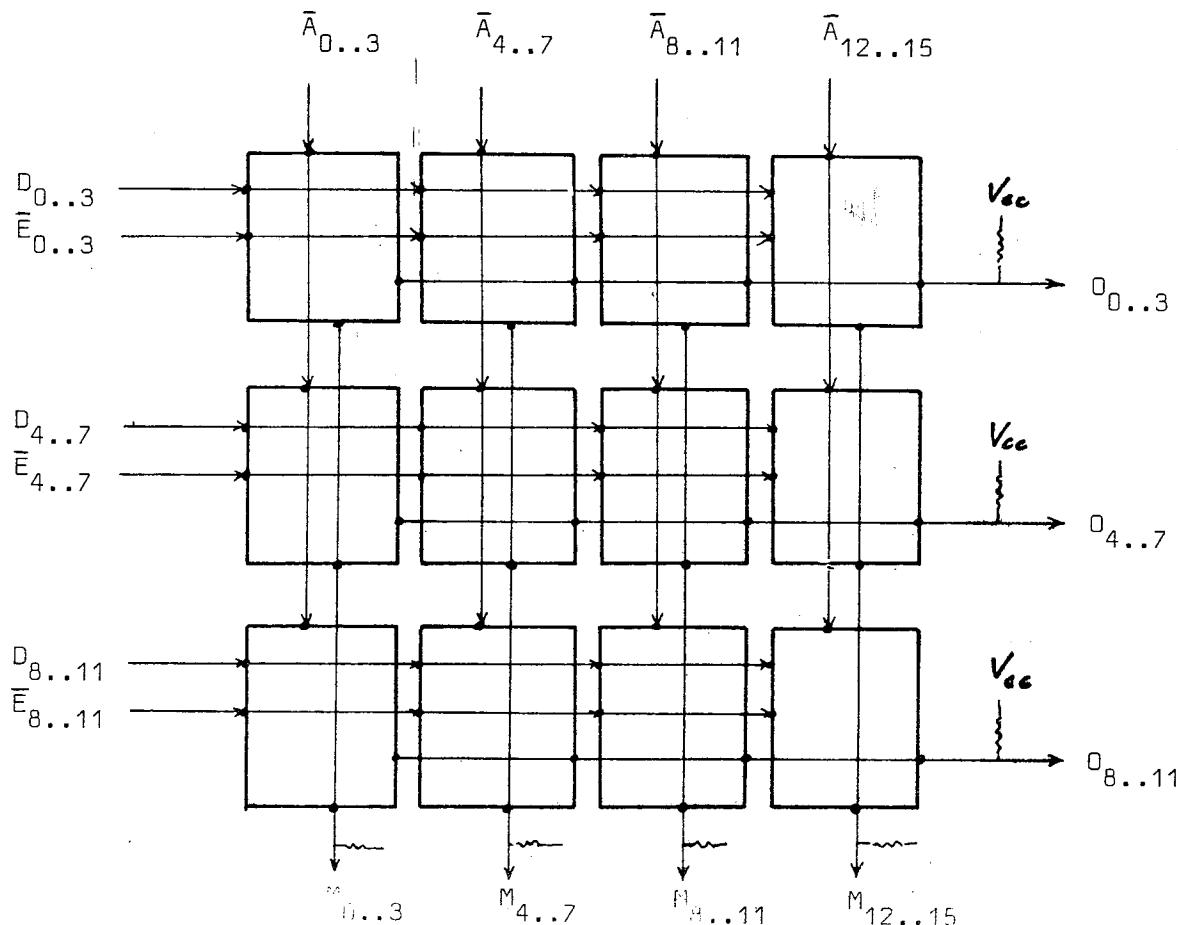

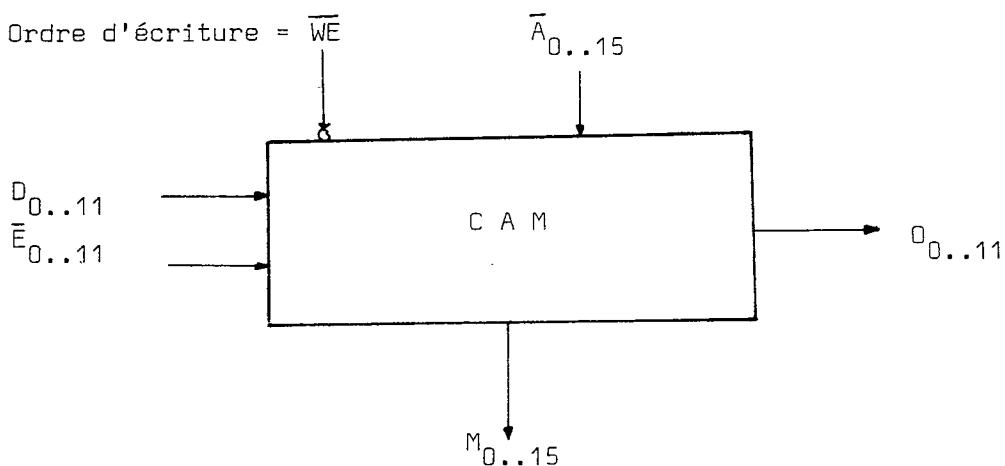

Se pose cependant la question de comptabilité avec les mécanismes d'adressage virtuel généralement utilisés dans les systèmes IRIS 80 classiques, qui décomposent la Mémoire Centrale en "pages" de 2 K octets: dans chaque Unité Centrale IRIS 80, une Mémoire Associative de 16 mots permet d'obtenir directement les numéros de 16 pages réelles associées au programme en cours d'exécution.

Comme nous le verrons plus loin, la machine PASC-HLL, à cause de son organisation "pipeline", ne peut pas se permettre de trouver une "faute de page" lors d'un accès à la Mémoire Centrale, parce qu'elle serait alors incapable de sauvegarder son contexte: au contraire, son mode de fonctionnement impose que toutes ses données soient présentes en Mémoire Centrale. Il est donc indispensable que le système d'exploitation bloque un certain nombre de "pages" réelles contenant les données utilisées par PASC-HLL.

S'il est impossible au système d'exploitation de compacter toutes les données relatives à un programme dans le même bloc physique, nous pouvons envisager une solution intermédiaire qui consiste à planter chacune des quatre zones de données (voir plus loin la définition de ces zones) utilisées par PASC-HLL dans des ensembles de pages réelles contigües, dont le nombre dépend de la taille réelle de ces zones.

Les données relatives à un programme seraient alors implantées dans des blocs physiques différents en Mémoire Réelle, et des conflits d'accès pourraient alors se produire, qui auraient pour effet de ralentir les deux Unités Centrales ainsi que les Unités d'échange, donc de diminuer les performances du système global.

Une étude importante reste donc à faire pour étudier une connexion éventuelle à un ordinateur IRIS 80, qui a été choisi comme exemple à cause de son existence à GRENOBLE et de la facilité technique de connexion à sa mémoire.

De plus, la définition d'un nouveau système d'exploitation reste à faire, qui permettrait d'envisager de nouvelles techniques d'exploitation basées sur la notion de multiprogrammation fonctionnelle plutôt que sur celle de multiprogrammation aléatoire dirigée par l'occurrence de "fautes de page" ou de "tranches de temps".

## B - L'ESPACE D'ADRESSAGE DE LA MACHINE

Nous abordons ici un des aspects "système" de la machine PASCALE. Afin de rendre plus aisée et plus souple la connexion de la machine avec la Mémoire Centrale gérée par le système d'exploitation "hôte", nous l'avons dotée d'un processeur d'interface avec la Mémoire Centrale. Ce processeur est appelé Processeur Mémoire et noté PME.

### I.- STRUCTURATION DE L'ESPACE D'ADRESSAGE

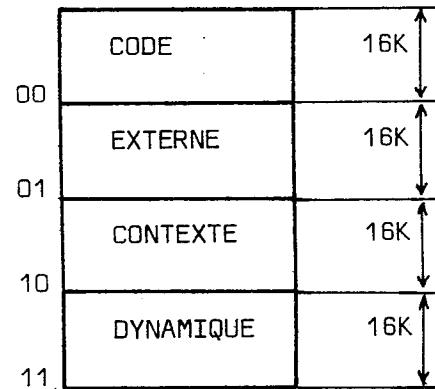

Les processeurs composant la machine (PINS, POP et PAC) adressent les informations dans un espace d'adressage virtuel composé de quatre zones.

La première zone, appelée CODE, contient toutes les informations en lecture seule générées par le compilateur: la table des TYPES, la table des CONSTANTS, le code des procédures.

La seconde zone, appelée EXTERNE, contient les mêmes informations que la zone CODE, informations qui sont relatives aux modules externes issus de compilations séparées. C'est sur cette zone que s'effectue le recouvrement (OVERLAY) des modules externes.

La troisième zone, appelée CONTEXTE, contient la pile de contexte de l'exécution du programme et reflète l'imbrication dynamique des procédures.

La dernière zone, appelée DYNAMIQUE, est réservée à l'allocation dynamique des données.

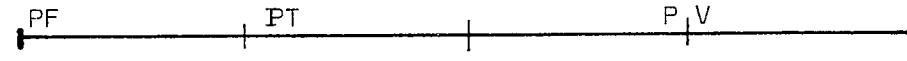

## II.- ADRESSAGE DES QUATRE ZONES DE L'ESPACE VIRTUEL

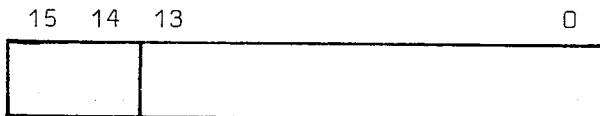

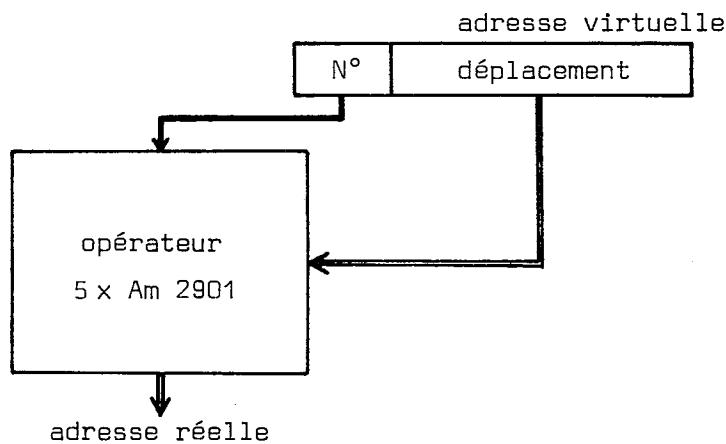

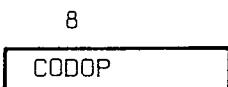

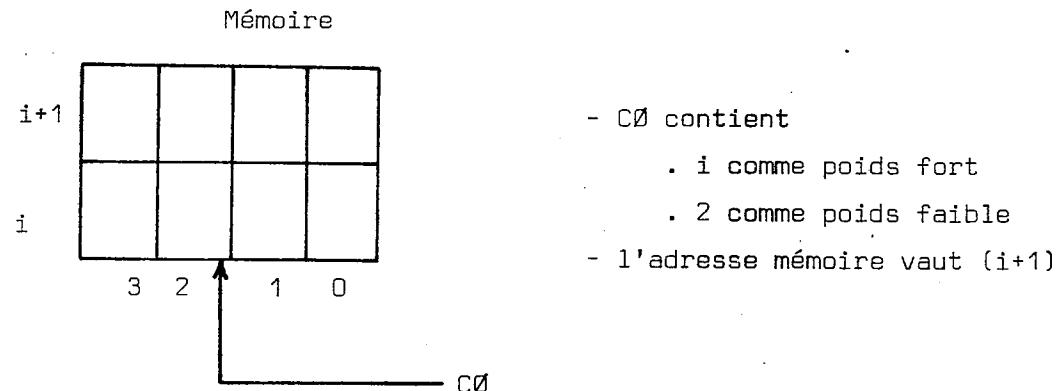

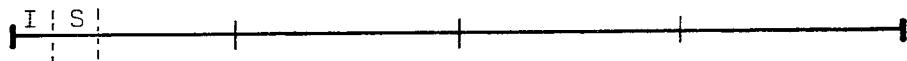

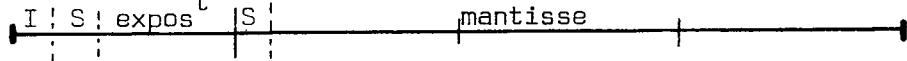

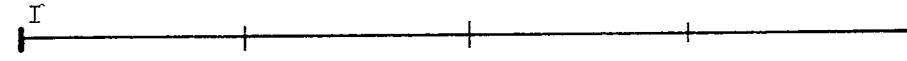

II.1. Chacun des processeurs (PINS, POP et PAC) sait dans quelle zone il désire lire ou écrire une information. Il envoie donc une adresse de la forme suivante:

où les bits 14 et 15 indiquent le numéro de la zone, et les bits 0 à 13 le déplacement dans cette zone.

On remarque que chaque zone peut contenir jusqu'à 16 Kmots (14 bits de déplacement).

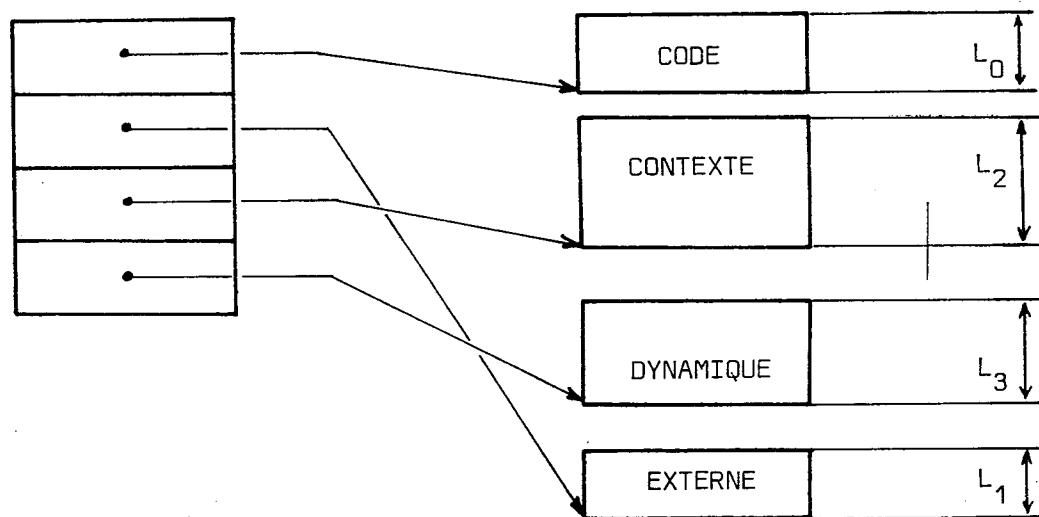

II.2. Le processeur PME reçoit donc une adresse virtuelle. Il la convertit en une adresse réelle de la manière suivante:

Lors de l'initialisation d'un travail, le système d'exploitation fournit à une adresse fixe, une table des zones réelles, qui décrit l'implantation réelle des quatre zones en Mémoire Centrale.

Cette table contient, pour chaque zone, l'adresse de son implantation et sa longueur.

|   | adresse réelle | longueur |

|---|----------------|----------|

| 0 |                |          |

| 1 |                |          |

| 2 |                |          |

| 3 |                |          |

Table des zones réelles

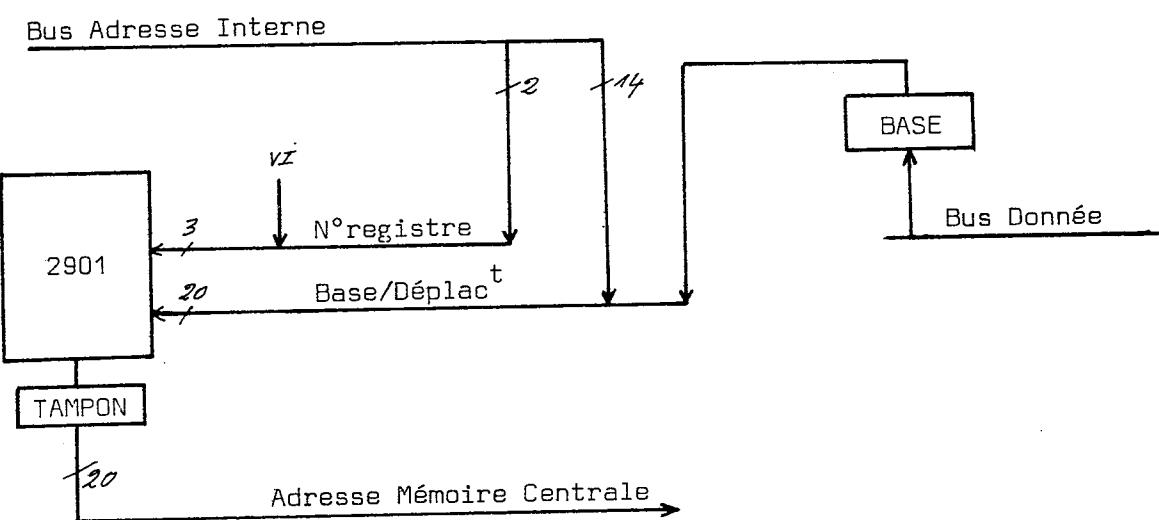

Le processeur PME, qui dispose d'un opérateur Am 2901 de 20 bits, initialise quatre registres de base avec les adresses réelles des quatre zones.

Ainsi, pour toute opération de Lecture/écriture en Mémoire Centrale demandée par l'un des processeurs PINS, POP ou PAC, le processeur PME effectue:

- 1/ une translation dynamique d'adresse par l'opération

BASE(N°ZONE) + DEPLACEMENT

- 2/ une protection en écriture pour les deux zones CODE et EXTERNE, qui ne contiennent que des informations en lecture seule.

Remarque :

Si le processeur PME détecte une tentative d'écriture dans l'une des zones CODE ou EXTERNE, il arrête l'exécution et avertit le système du fait qu'un processeur de la machine PASCALE commet une erreur grave et se trouve donc en panne.

### II.3. Avantages

- 1/ Le premier avantage consiste en le fait que le système d'exploitation "hôte" peut planter chacune des quatre zones n'importe où dans la Mémoire Centrale, en fonction de sa gestion propre et de la taille de chacune des zones.

- 2/ Le second avantage est relatif à la taille variable des quatre zones:

- la taille de la zone CODE est parfaitement connue: elle est donnée par le compilateur.

- la taille de la zone EXTERNE est celle du module EXTERNE présent en mémoire centrale: elle peut donc changer lorsqu'on change de module externe, mais là encore sa taille est donnée par le compilateur.

- la taille de la zone CONTEXTE est fonction de la complexité du programme (imbrication dynamique des procédures) et du nombre de variables manipulées. Elle sera donc définie par le programmeur, lorsqu'il demande l'exécution de son programme: c'est un paramètre d'une "instruction-système".

- la taille de la zone DYNAMIQUE est elle aussi dépendante des données manipulées: elle peut être nulle dans le cas où le programmeur ne fait aucune allocation dynamique. Ce sera également un paramètre d'une "instruction-système".

- 3/ Enfin, toutes les informations relatives à un travail sont translatables: elles peuvent être implantées par le système d'exploitation n'importe où en mémoire, et changer de place selon les besoins du système (une zone peut être sauvegardée sur disque par le système et remise en mémoire à une adresse différente).

**Mémoire virtuelle de la

Machine PASCALE**

Espace virtuel:

Espace réel:

**Mémoire Réelle du

système "HOTE"**

Processeur PME

### III.- ORGANISATION DES ZONES CODE et EXTERNE

La zone CODE contient le module Principal généré par le compilateur.

Son organisation a été conçue:

- 1/ pour faciliter le travail du compilateur,

- 2/ pour permettre une édition de liens facile et rapide entre le Module Principal et les Modules Externes,

- 3/ pour permettre l'exécution de procédures externes.

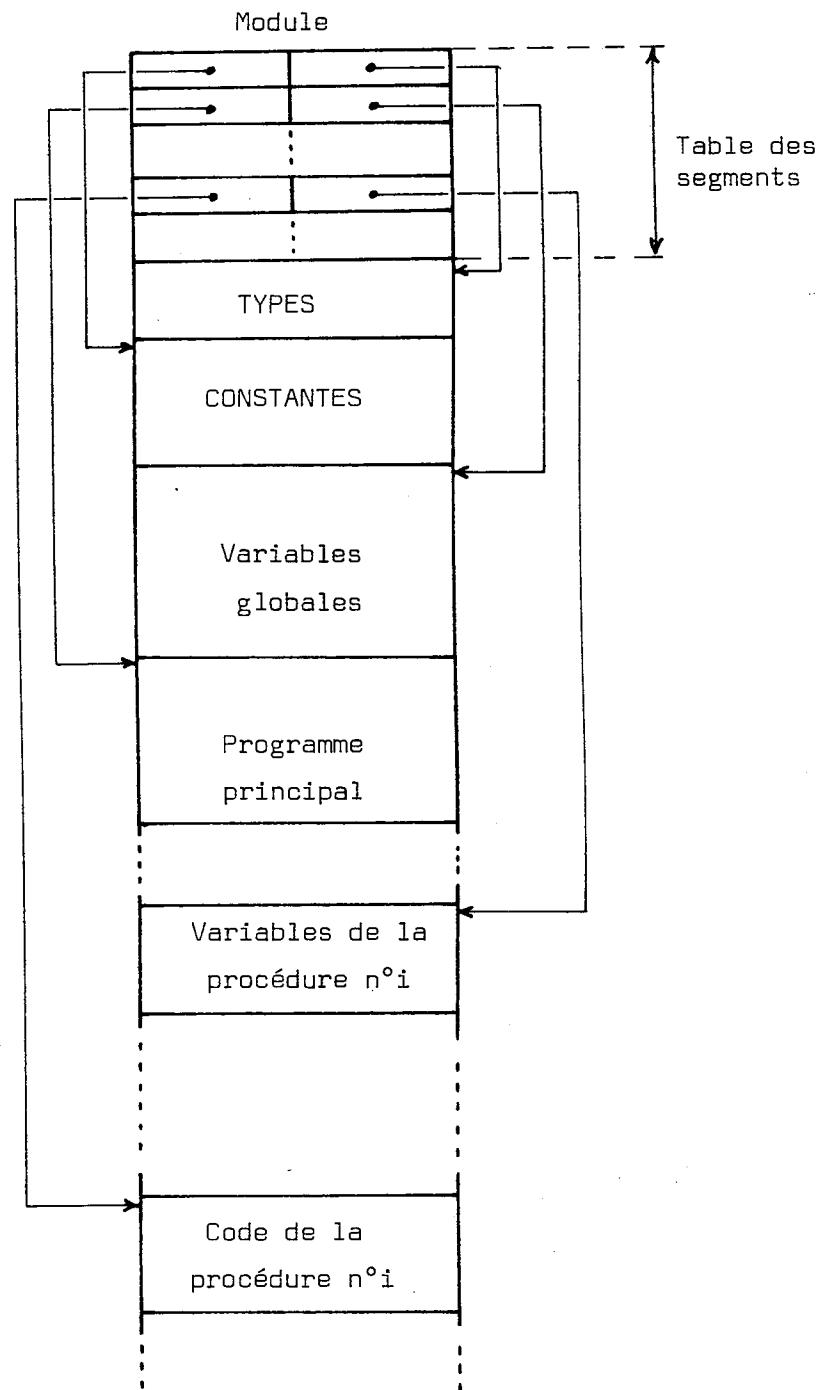

#### III.1. Résultat d'une compilation

Au cours du processus de compilation, plusieurs catégories d'informations sont générées:

- une table des TYPES construite conformément aux déclarations de types,

- une table des CONSTANTES,

- les descripteurs de paramètres et de variables pour chaque procédure,

- enfin, le code-machine pour chaque procédure.

Toutes ces informations sont regroupées, à la fin du processus de compilation, sous la forme d'un Descripteur de Module, contenant les adresses des fichiers construits.

### III.2. Chargement d'un module

Avant de pouvoir exécuter un module, toutes les informations qui le composent sont lues sur disque et chargées en Mémoire Centrale: on obtient ainsi un Module exécutable, qui est chargé soit dans la zone CODE, soit dans la zone EXTERNE, selon l'organisation suivante:

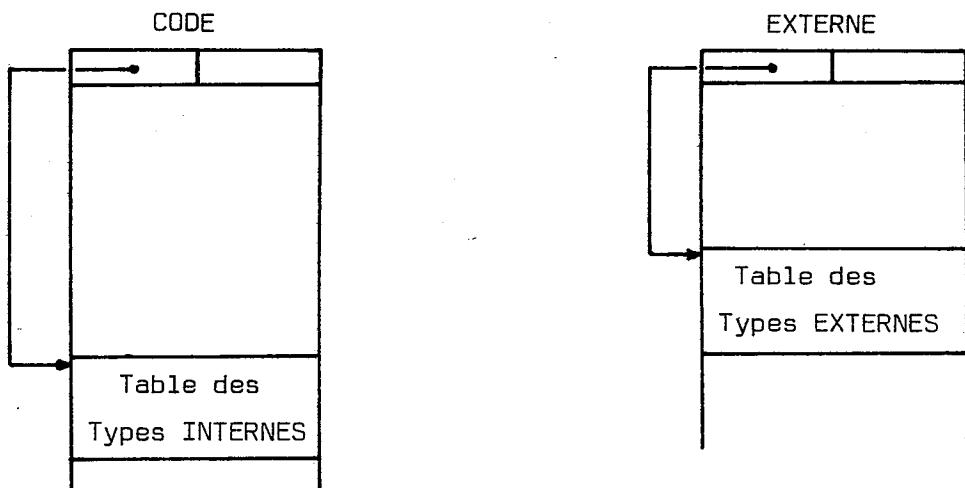

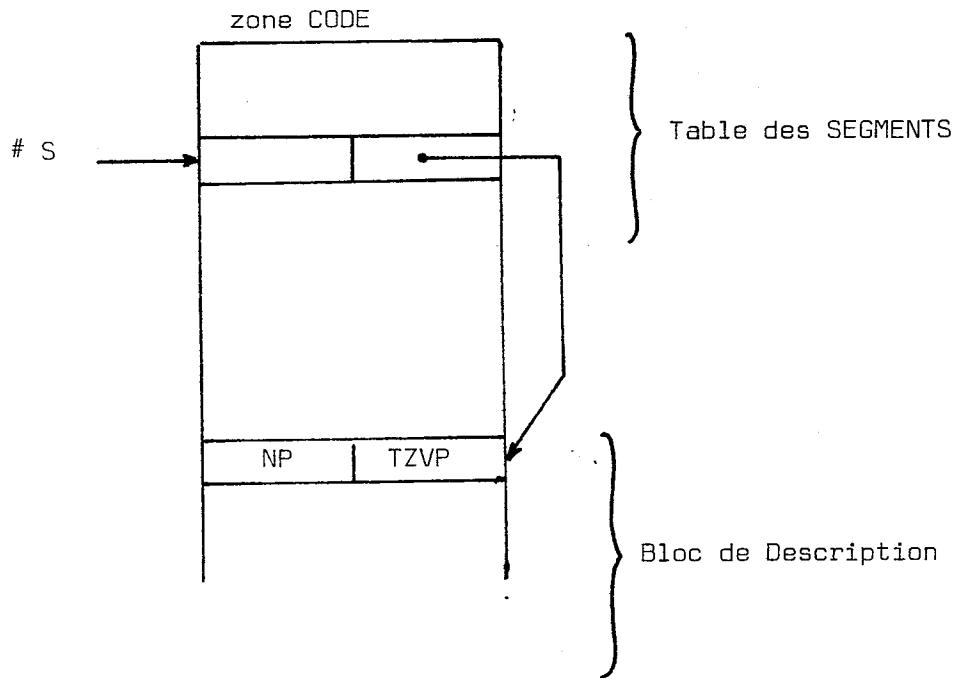

Les N premiers mots d'un MODULE constituent la TABLE DES SEGMENTS de ce module.

. le premier mot de la table des segments (déplacement =0) contient l'adresse relative de la table des TYPES et celle de la table des CONSTANTES (ces deux adresses sont lues par le processeur POP pour construire l'adresse d'un descripteur de type ou celle d'une constante).

. le (i+1)ième mot de la table (déplacement=i) contient les informations relatives à la procédure n°i (i est le paramètre des instructions CALL pour PAC et ENTER pour POP).

Remarque:

On aurait pu réaliser une segmentation réelle pour les procédures, mais les problèmes posés par les modules externes sont dans ce cas insolubles. Les différents segments (procédures) sont donc supposés être chargés dans une zone continue (CODE ou EXTERNE).

III.3. Adressage des procédures externes

1/ définition des compilations séparées

Nous avons choisi, en accord avec d'autres concepteurs de compilateur PASCAL ([ ]), de prévoir la notion de compilations séparées de plusieurs morceaux d'un même programme.

L'organisation choisie, voisine de celle de PL/1, est caractérisée par l'existence d'un Module Principal, défini par l'entête:

PROGRAM <NOM> ;

programme PASCAL

Dans la description d'un tel programme, peuvent apparaître des déclarations de procédures "externes" sous la forme suivante:

procédure <NOM> {<liste de paramètres>} ; PASCAL ;

Plusieurs procédures (ou fonctions) "externes" peuvent ainsi être déclarées et sont normalement "appelées" dans le programme principal.

Ces procédures (ou fonctions) "externes" appartiennent à des Modules Externes qui sont compilés séparément. La structure d'un Module Externe est la suivante:

- sa description ne commence pas par le mot-clé program mais par EXTERN <NOM> ;

Aucune déclaration de variables globales ne peut être faite, mais par contre des types peuvent être déclarés, qui sont propres à ce module (la déclaration de types est indispensable pour la description des paramètres).

Viennent ensuite des déclarations de procédures (ou de fonctions) dont les noms sont ceux des "points d'entrée" dans le module externe.

Ainsi, dans l'exemple suivant:

```

EXTERNE TRIGO ;

TYPE

|

function SIN(---): real ;

|

function COS(---): real ;

|

```

le module TRIGO a deux points d'entrée qui ont pour noms SIN et COS.

## 2/ édition de liens et chargement

Le travail de l'éditeur de liens consiste à mettre à jour la table des segments du module principal.

Résultat de la compilation du Module principal

Le compilateur fournit la table des externes.

| NOM  | #S |

|------|----|

| TOTO | 4  |

| JOJO | 5  |

| MOMO | 8  |

| KOKO | 10 |

Résultat de la compilation des modules externes

Le compilateur fournit une table des entrées pour chaque module.

Module 1

| NOM  | #S |

|------|----|

| KOKO | 1  |

| TOTO | 4  |

| MOMO | 15 |

Module 2

| NOM  | #S |

|------|----|

| JOJO | 1  |

Mise à jour de la table des segments du Module Principal

(au moment du chargement du Module principal)

|            |   |      |       |

|------------|---|------|-------|

| TOTO → #4  | 1 | #M=1 | #S=4  |

| JOJO → #5  | 0 | #M=2 | #S=1  |

| MOMO → #8  | 1 | #M=1 | #S=15 |

| KOKO → #10 | 1 | #M=1 | #S=1  |

Dans l'exemple, le module #1 est chargé dans la zone EXTERNE.

### 3/ liaison avec un module externe

Toute procédure déclarée "EXTERNE" dans le programme principal est affectée d'un numéro de segment et occupe un mot dans la table des segments du module principal.

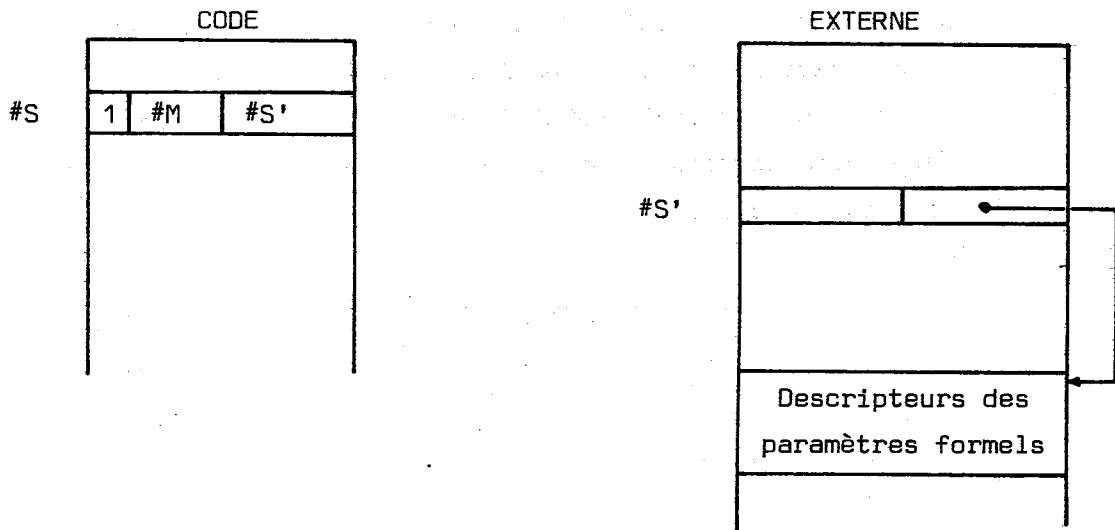

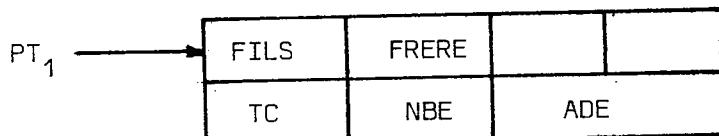

Lorsque le processeur PINS reçoit une instruction CALLEXT(i), il accède au descripteur de segment n°i qui contient les informations suivantes:

| segment n°i | P | #M | #S |

|-------------|---|----|----|

|-------------|---|----|----|

- un indicateur de présence P dont la valeur "1" indique que le module #M a bien été chargé dans la zone EXTERNE.

- le n° du module externe #M qui contient la procédure externe.

- le n° #S du segment de la procédure dans le module externe.

En cas d'absence du module (P=0), le processeur PINS envoie une instruction de sauvegarde vers ses deux esclaves PAC et POP et avertit le système qu'il s'est produit une "faute de module externe" n° #M.

Le système est supposé capable de trouver l'adresse disque d'un module et de mettre à jour la table des segments du module principal.

### 4/ adressage des types et des constantes

La difficulté provient du fait des compilations séparées: les descripteurs de types peuvent appartenir à deux zones différentes, la zone CODE pour les types de programme principal, la zone EXTERNE pour les types d'une procédure externe, et le même problème se pose pour les constantes.

#### 4.1. nécessité de vérification des types de paramètres

Supposons qu'une procédure soit déclarée "externe" de la manière suivante:

(D1)      procédure PEXT (P1: <type1> ; P2 : <type2>) ; PASCAL ;

Dans le module externe, compilé séparément, sa déclaration comme "point d'entrée" est:

(D2)      procédure PEXT (P'1: <type'1> ; P'2: <type'2>) ;

Sachant qu'il n'y a aucun lien entre deux compilations séparées, on ne peut que vérifier, au cours de la compilation du programme principal, qu'un appel "PEXT (<exp1>, <exp2>);" est compatible avec la déclaration (D1).

Au moment de l'exécution de cet appel de procédure, nous devons donc prévoir une vérification de la compatibilité des types des paramètres ainsi que de leur nombre. La seule solution consiste à prendre les descripteurs des paramètres formels dans le module externe, afin de vérifier dynamiquement qu'il y a bien compatibilité.

#### 4.2. réalisation de l'appel d'une procédure externe

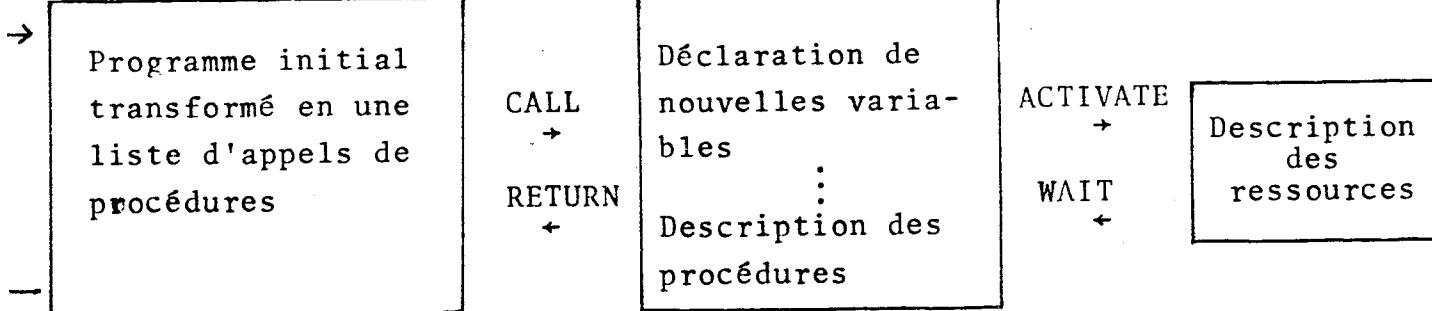

Lorsque le compilateur analyse une instruction d'appel de procédure, il sait si celle-ci est interne ou externe. Dans le 2ème cas, il génère les instructions suivantes:

```

pour PEXT(<exp1>, <exp2>) ;

CALL-EXT #S(PEXT)

<exp1>

PARAM-EXT SP, -3

<exp2>

PARAM-EXT SP, -4

ENTER-EXT #S(PEXT)

```

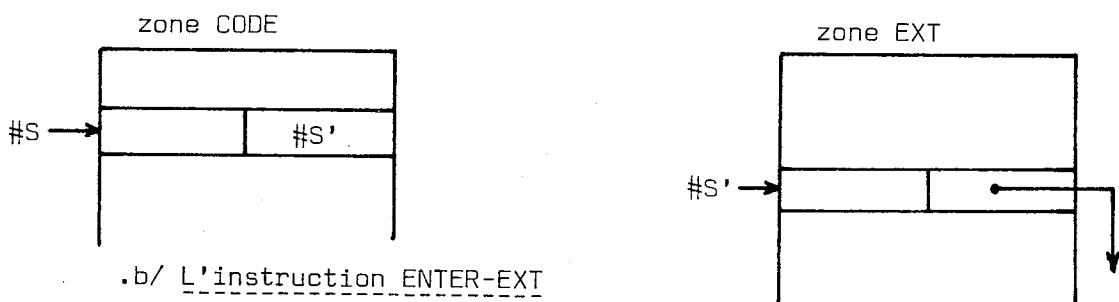

1) l'instruction "CALL-EXT(#S)" est accédée par le processeur PINS, qui accède au segment #S localisé à l'adresse #S dans la zone CODE.

Si le bit de présence vaut '1', alors l'exécution peut continuer puisque le Module externe qui contient PEXT est présent en Mémoire centrale.

Dans le cas contraire, l'exécution est arrêtée: des instructions de sauvegarde du contexte sont envoyées à PAC et à POP et le système est averti par PINS qu'il y a "faute du module #M".

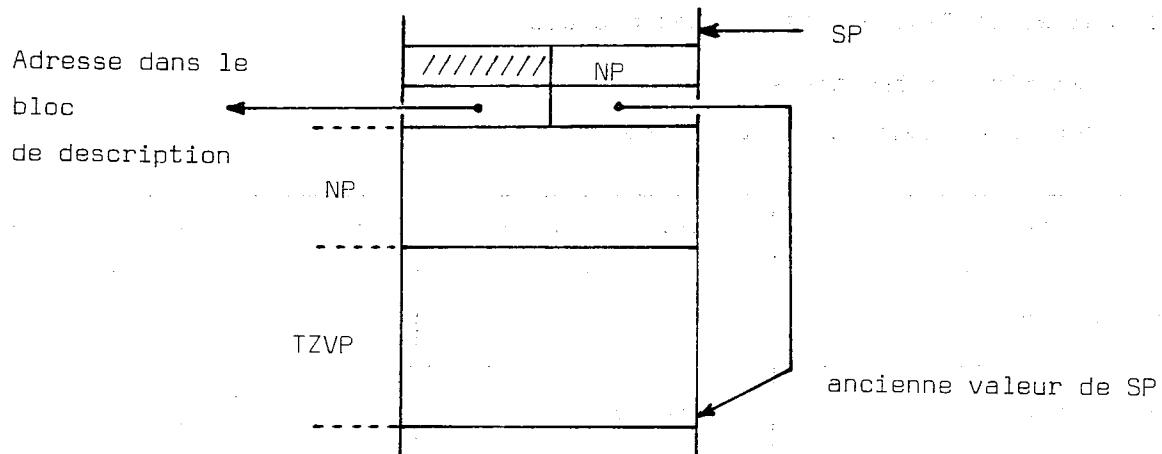

2) l'instruction "CALL-EXT(#S)" est reçue par le processeur PAC uniquement si le module #M est présent. Le descripteur de segment principal #S

contient le numéro #S' du segment externe. Cette indirection permet à PAC d'accéder aux descripteurs des paramètres formels déclarés dans la procédure externe.

Ces descripteurs de paramètres formels sont recopier sur la pile de contexte (zone CONTEXTE).

3) le processeur POP reçoit l'instruction PARAM-EXT. Le suffixe "EXT" lui indique que le descripteur de type du paramètre se trouve dans la table des types externe, dont l'adresse est donnée par le segment n°0.

4) le processeur PINS accède l'instruction ENTER-EXT(#S). Il accède au segment n°#S dans la table des segments principales, qui lui donne le n°#S'

du segment de la procédure externe, qui contient l'adresse du code de cette procédure. Il passe en mode "EXTERNE", c'est-à-dire que toutes les instructions seront accédées dans la zone EXTERNE et il continue l'exécution, en envoyant l'instruction ENTER-EXT aux deux processeurs PAC et POP.

5) le processeur PAC reçoit l'instruction ENTER-EXT. Il a noté dans la pile de contexte l'adresse, dans la zone EXTERNE, des descripteurs des variables de la procédure externe. Il les recopie sur la pile de contexte et passe en mode "EXTERNE".

6) le processeur POP reçoit l'instruction ENTER-EXT. Il accède au segment #0 du module externe, qui contient la base des types externes et la base des  constantes externes. Il mémorise ces deux bases dans deux registres internes et passe en mode EXTERNE.

#### 4.3. réalisation du retour d'une procédure externe

Lors de la compilation d'un module externe, toute fin de procédure du premier niveau (point d'entrée externe), conduit à la génération de l'instruction RETURN-EXT.

##### 1) le processeur PINS accède à l'instruction RETURN-EXT

Il sort alors du mode EXTERNE et retourne dans le segment appelant du module principal.

##### 2) le processeur PAC reçoit l'instruction RETURN-EXT

Il sort du mode EXTERNE et réalise un retour normal de procédure en mettant à jour la pile de contexte et les chainages statiques et dynamiques.

##### 3) le processeur POP reçoit l'instruction RETURN-EXT

Il remet à jour les bases des types et des constantes en allant lire leur valeur dans le segment #0 du module principal, puis il sort du mode EXTERNE.

Remarque: dans le mode EXTERNE, les trois processeurs adressent la zone EXTERNE pour l'accès aux descripteurs de segments, de types, de paramètres et de variables et aux constantes.

#### 4.4. problèmes propres aux fonctions externes

Supposons la déclaration suivante:

dans le programme principal:

function F(P1: <type1>) : <type2> ; PASCAL ;

et dans le module externe:

function F(P': <type'1>) : <type'2>;

begin

code

F := <expression>

end ;

Le résultat d'une fonction est passé en paramètre par référence.

Ainsi, dans le programme principal, le compilateur crée une variable, appelée F, dont le type est <type2>.

Tout appel de la fonction F (par exemple F(<exp>)) donne lieu à la génération de:

Call-Ext (#S)

Id F

Param-Ext SP,-3

<exp>

Param-Ext SP,-4

Enter-Ext (#S)

Nom F

Lors du passage du premier paramètre, le processeur POP peut ainsi vérifier qu'il y a compatibilité entre <type2> donné par le descripteur de F et <type'2> donné par le descripteur du paramètre formel, résultat de la fonction.

Le passage de paramètre par référence permet de plus de transmettre la valeur du résultat de la fonction depuis le module externe par l'instruction AFFECT LOC,-3 générée à l'occurrence de F := <expression>.

#### IV.- ORGANISATION DE LA ZONE CONTEXTE

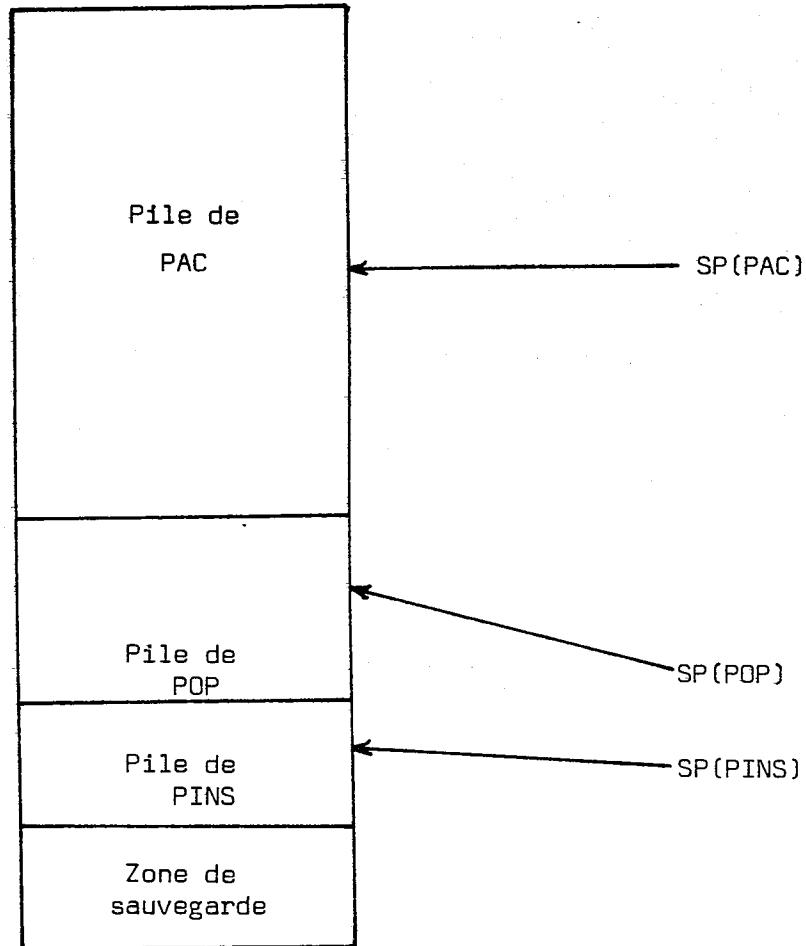

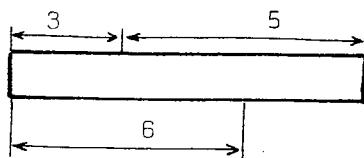

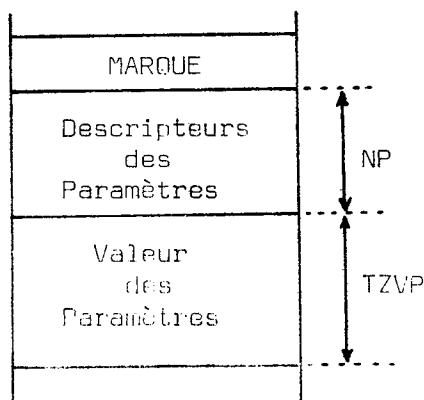

Les trois processeurs PINS, PAC et POP utilisent une pile. Ces trois piles sont implantées dans la zone CONTEXTE.

- le processeur PINS empile et dépile des descripteurs de contrôle des segments du programme

- le processeur POP empile et dépile des résultats intermédiaires longs ainsi que des descripteurs de contrôle de boucle (valeur courante et valeur limite de l'indice)

- le processeur PAC gère la pile de contexte selon l'imbrication des procédures (cette pile contient les variables des procédures et les marques de blocs)

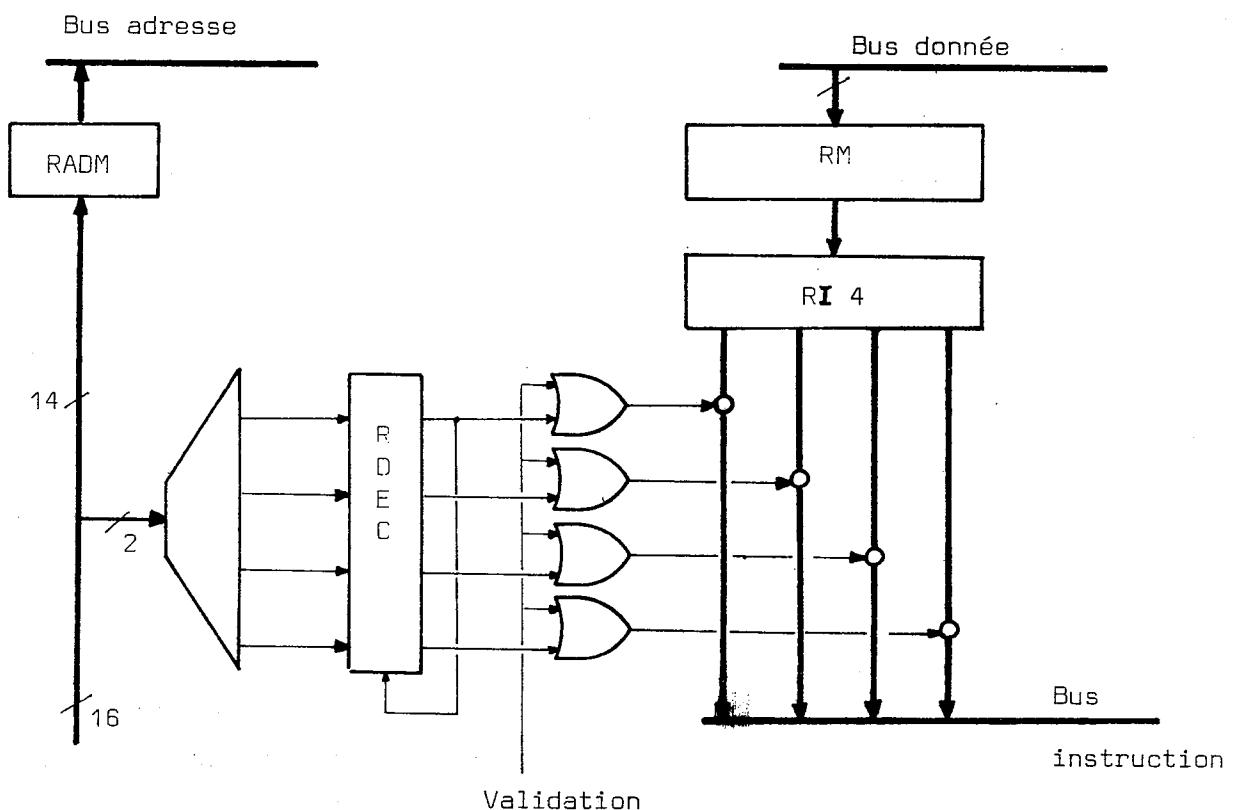

Ces trois piles sont adjacentes en Mémoire Centrale et les processeurs PINS et POP disposent d'une pile interne de 16 mots (RAM).

Une zone fixe, située "en bas" de la zone CONTEXTE, permet de sauvegarder les adresses des sommets des piles et les registres de base en ce qui concerne le processeur PAC.

Image de la zone CONTEXTE au cours de l'exécutionInitialisation par le système

La valeur initiale de la zone de sauvegarde est chargée par le système avec:

SP(PINS) = <taille Z de sauvegarde

SP(POP) = <SP(PINS) + Taille Pile(PINS)

SP(PAC) = <SP(POP) + Taille Pile(POP)

W(PAC) = 0

B0(PAC) = <SP(PAC) + Taille Var-Prédéfinies>

B2(PAC) = ... = B6(PAC) = 0

Les valeurs de la base des types et de la base des constantes du Module Principal sont également chargées en adresse #2.

#### Sauvegarde par les processeurs

Lorsque PAC et POP reçoivent de la part de PINS une instruction de sauvegarde complète, ils écrivent les informations précédentes dans la zone de sauvegarde, après avoir vidé leur pile interne en mémoire centrale.

#### Restauration du contexte

Dans un but de simplification, la restauration d'un contexte doit être identique à l'initialisation première. Cela suppose donc que le processeur PINS trouve au sommet de sa pile l'adresse de la première instruction à exécuter, c'est-à-dire l'appel du programme principal dans le cas de l'initialisation: cette instruction d'appel est générée par le compilateur, c'est le point d'entrée, dont l'adresse est mise par le système comme sommet de pile du processeur PINS.

#### Séquence initiale d'instructions

```

→ CALL i

ENTER i

HALT

```

i représente le n° du segment principal du programme

adresse fournie par le système

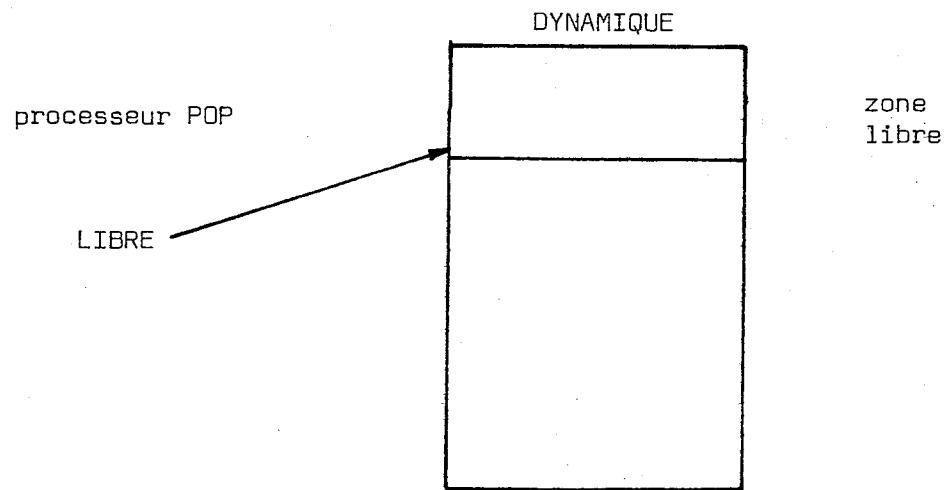

## V.- ORGANISATION DE LA ZONE DYNAMIQUE

La zone DYNAMIQUE est réservée à l'allocation dynamique de variables au cours de l'exécution d'un programme.

Le langage PASCAL permet la création d'espaces en mémoire pour contenir des informations repérées par des POINTEURS. Tout pointeur est déclaré comme étant une variable dont la valeur représente l'adresse de l'élément pointé et il est caractérisé par le type de cet élément.

Ainsi, on déclare:

var P : ↑<type>

et l'élément pointé par P est de type <type>.

V.1. L'allocation dynamique est commandée par l'instruction

NEW(P) ;

de PASCAL. Cette instruction peut spécifier des paramètres supplémentaires sous la forme

NEW(<pointeur> , <liste d'aiguillages>) ;

où la <liste d'aiguillage> définit le choix de branches successives dans une structure RECORD qui peut avoir plusieurs branches sous la forme d'une arborescence. (voir opérateur NEW, chapitre POP)

Cette liste d'aiguillage a pour but de spécifier un sous-type du type RECORD et définit dynamiquement la taille de l'élément ainsi créé.

V.2. La libération d'espace est commandée par l'instruction DISPOSE (<pointeur>), qui spécifie la libération de toute la zone située "au dessus" du mot pointé par le <pointeur>. (voir opérateur DISPOSE, chapitre POP)

V.3. Adressage de la zone DYNAMIQUE

La zone DYNAMIQUE est adressée uniquement par le processeur POP, au moyen de "pointeurs", lorsqu'il accéde à la valeur des éléments "pointés".

Les mouvements du pointeur LIBRE sont commandés par les instructions NEW et DISPOSE qui respectivement, créent et libèrent des éléments dans la zone.

La valeur de ce pointeur est évidemment sauvegardée en Mémoire Centrale par le processeur POP lorsqu'un changement de contexte se produit.

## C - LES ENTREES-SORTIES

### INTRODUCTION

Tout programme écrit en langage évolué fait obligatoirement référence à au moins un fichier de sortie, qui contiendra les résultats exploitables de l'exécution du programme.

Le langage PASCAL fournit au programmeur deux fichiers prédéclarés (INPUT et OUTPUT) qui correspondent à un "fichier-carte" et un "fichier-imprimante". On peut cependant déclarer d'autres fichiers, de la manière suivante:

<nom de fichier> : FILE OF <type>.

Le premier problème consiste à définir un lien entre l'exécution du programme et le système d'exploitation: ce lien est établi par le numéro du fichier, défini par l'ordre des déclarations des fichiers dans le programme, et constitue un des paramètres de l'appel du système d'exploitation par la machine PASCALE, un autre paramètre donnant évidemment la nature de l'opération d'entrée/sortie demandée au système.

Cet appel au système est réalisé par une "interruption" lancée vers la machine "hôte" qui exécute le Système.

## I.- STRUCTURE DES INFORMATIONS

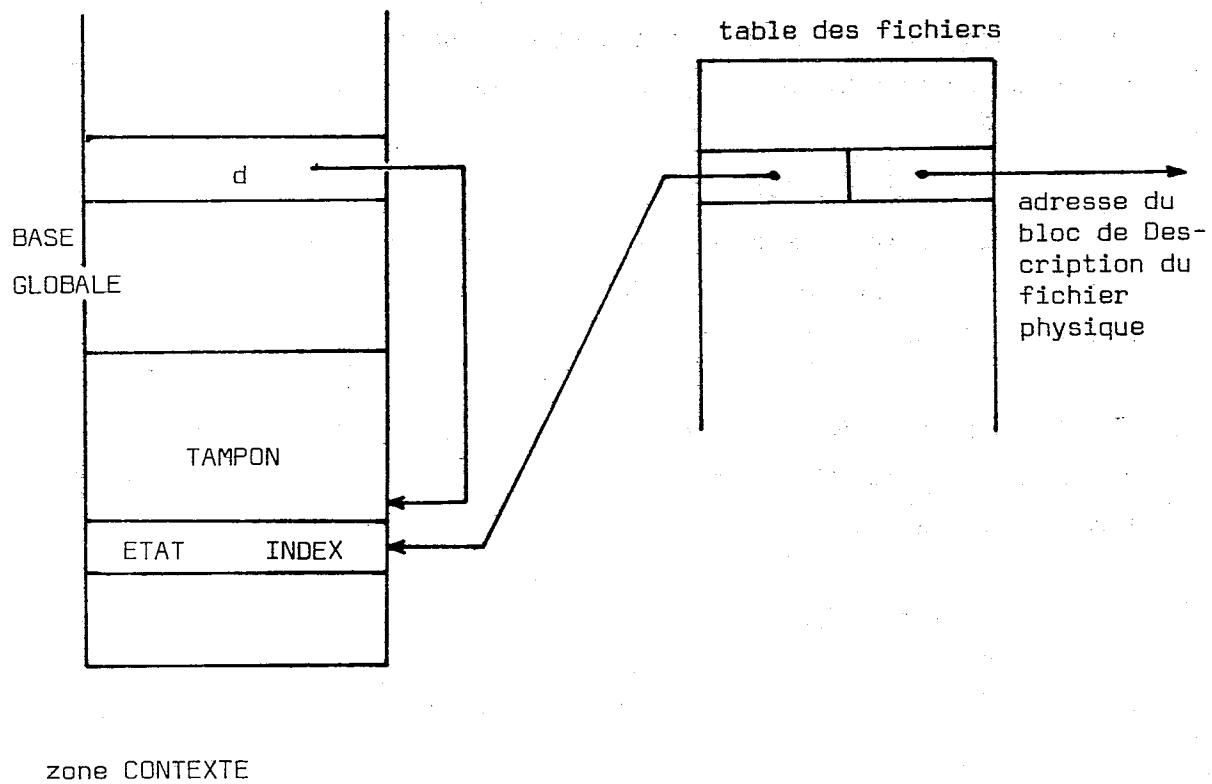

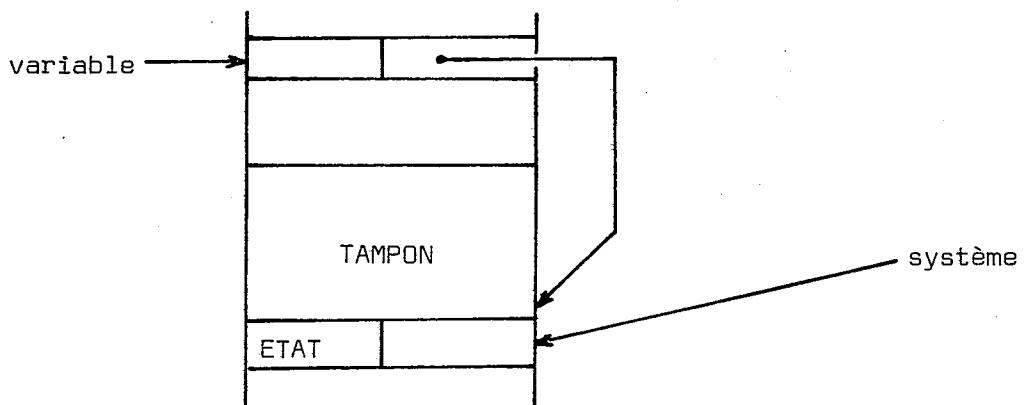

### I.1. Aspect système

Le système d'exploitation possède une table des fichiers relatifs au programme principal. Cette table contient deux éléments:

1/ l'adresse du TAMPON qui contient la valeur du dernier élément du fichier accédé (ce TAMPON est localisé dans la zone CONTEXTE, en adresse basse).

2/ l'adresse d'un BLOC DE DESCRIPTION du fichier. Ce bloc, exploité par le système d'entrée/sortie, contient toutes les informations nécessaires à la méthode d'accès au fichier (adresse du périphérique, adresse sur le périphérique, mode d'accès, longueur d'un bloc, etc...).

### I.2. Aspect machine PASCALE

1/ Les ordres d'entrée/sortie émis par la machine PASCALE spécifient le numéro du fichier concerné. Ce numéro est utilisé par le système pour accéder au fichier par l'intermédiaire de la Table des Fichiers.

2/ Les accès à la valeur de l'élément du fichier sont faits par les processeurs PAC et POP par référence à une variable structurée, dont le champ PV est égal à l'adresse du TAMPON associé au fichier.

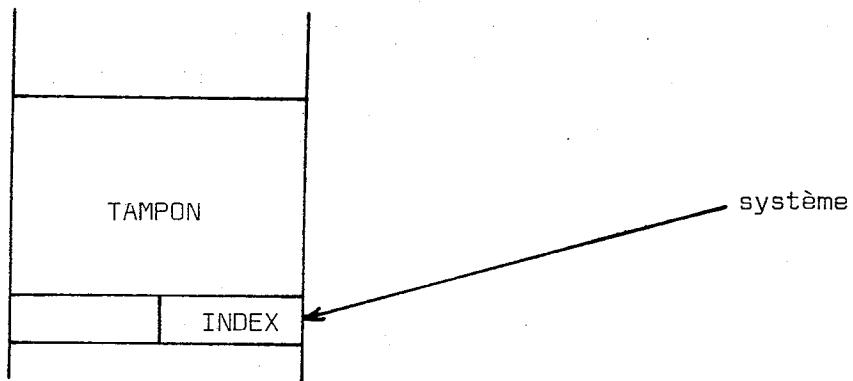

3/ Le test de la fin du fichier (fonction EOF) et la transmission de la valeur de l'index dans le cas de fichiers indexés, utilisent un MOT DE CONTROLE localisé dans le premier mot de TAMPON.

### 1.3. Adresse de la zone TAMPON

Pour chaque fichier déclaré (ou prédéclaré), la zone TAMPON, dont la taille est égale à la taille maximum d'un élément du fichier plus 1 mot de contrôle, est adressé à la fois par la machine PASCALE par l'intermédiaire de la variable associée au fichier, et par le système par l'intermédiaire de la table des fichiers, selon la figure

zone CONTEXTE

## II.- EXECUTION DES OPERATIONS D'ENTREE/SORTIE

Un programme écrit en langage évolué (PASCAL par exemple) contient des ordres d'entrées/sorties élémentaires et des accès à des éléments de fichiers.

Le programme demande un accès à l'élément suivant (GET(FICHIER)) puis référence l'élément fourni par le système (FICHIER $\uparrow$ ). Le travail de la machine langage qu'est la machine PASCALE se limite à détecter les ordres d'entrées/sorties et à les transmettre au système d'exploitation qui l'accueille.

### II.1. Détection des ordres d'entrée/sortie

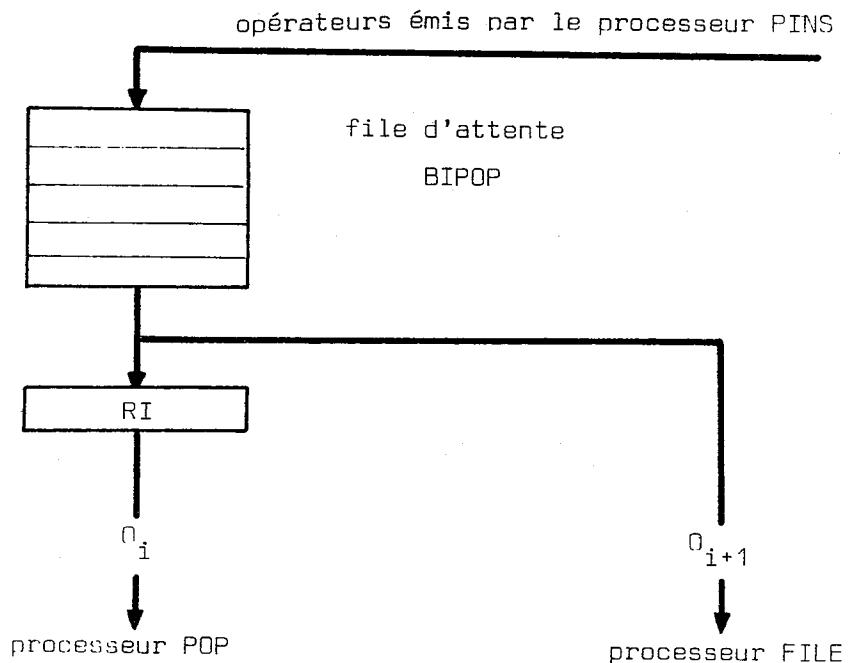

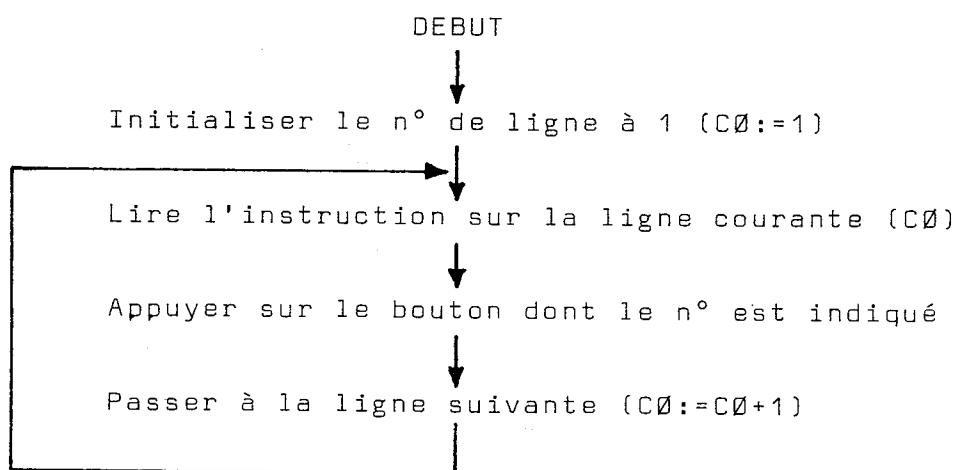

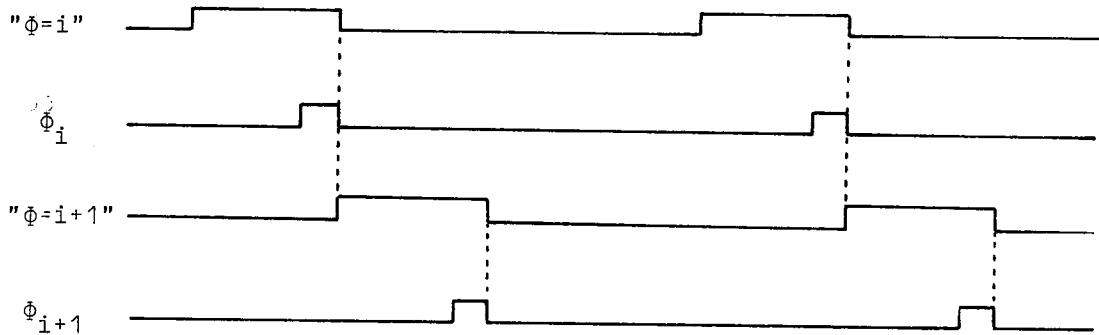

L'organisation "pipe-line" de la machine PASCALE fait apparaître un processeur maître, le processeur PINS qui est la première station du "pipe-line" et deux esclaves qui sont les processeurs PAC et POP.

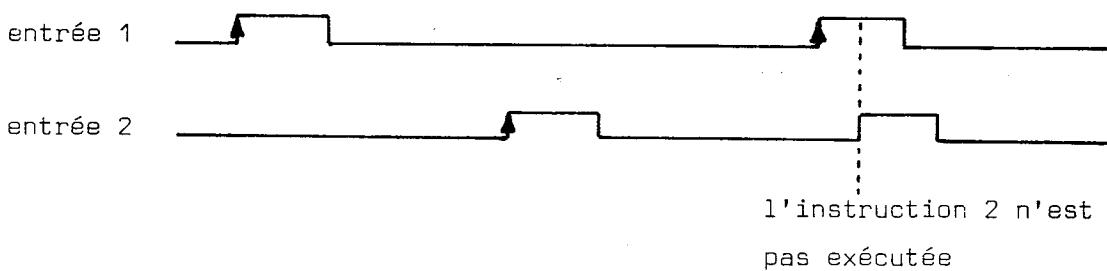

Problème: Est-il possible de confier à l'un des esclaves (PAC ou POP) la charge de détecter une condition d'arrêt de l'exécution? La réponse est négative. La preuve peut en être faite par l'absurde.

Supposons que PAC détecte une condition d'arrêt. A cet instant précis, sa file d'attente d'instructions n'est pas vide et le processeur PINS continue d'analyser les instructions suivantes: il lui est impossible de retrouver le contexte de l'instruction qui produit l'arrêt du processeur PAC et donc de préparer une sauvegarde du contexte général de la machine.

Conséquence: Tout arrêt de l'exécution d'un programme doit être commandé par la station maître du pipeline, en l'occurrence le processeur PINS.

En particulier, toute opération d'entrée/sortie doit être détectée par le processeur PINS.

### II.2. Les ordres d'entrée/sortie

Les ordres d'entrée/sortie élémentaires utilisés dans la machine PASCALE sont:

- GET n° fichier = lecture de l'élément suivant pour un fichier séquentiel ou lecture de l'élément dont la clef est égale à l'INDEX passé en paramètre pour un fichier indexé.

- PUTn° fichier = écriture de l'élément courant dans la position suivante pour un fichier séquentiel ou dans la position dont la clef est égale à l'INDEX passé en paramètre pour un fichier indexé.

- RESET n° fichier = remise au départ d'un fichier séquentiel.

- REWRITE n°fichier = passage en écriture d'un fichier qui était en lecture.

Ces quatre ordres sont envoyés par le processeur PINS au système d'exploitation, avec un paramètre égal au numéro du fichier. C'est le système qui exécute l'opération d'entrée/sortie, alors que la machine PASCALE sauvegarde son contexte et se met en attente d'un nouveau travail à exécuter.

#### II.3. Accès aux éléments des fichiers

Lorsqu'une opération d'entrée/sortie a été exécutée par le système d'exploitation, la machine PASCALE reprend l'exécution du programme dans lequel figurent des instructions d'accès (en lecture ou écriture) à l'élément courant du fichier. La variable associée au tampon du fichier est référencée comme n'importe quelle variable du programme et son type peut être quelconque. C'est un tableau de 80 caractères (par exemple) pour le fichier prédéclaré INPUT et 132 caractères (par exemple) pour le fichier prédéclaré OUTPUT.

#### II.4. Test de fin de fichier

Le programmeur dispose de la fonction EOF (fichier) qui est compilée en:

```

NOM <fichier>

EOF

```

où "EOF" est un opérateur binaire qui donne un résultat booléen.

Son opérande est un descripteur de variable, dont le champ "adresse de la valeur" pointe sur le TAMPON du fichier. A cette adresse moins 1, se trouve le mot de contrôle du fichier qui indique, en particulier, l'état "FIN DE FICHIER", état positionné par le système:

### II.5. Accès aux fichiers indexés

Le programmeur peut spécifier l'index de l'élément du fichier, sous la forme:

GET(<fichier>, <expression>) ou PUT(<fichier>,<expression>).

Cet appel de fonction est compilé en:

```

NOM <fichier>

<expression>

AFFINDEX

GET/PUT n° fichier

```

où AFFINDEX est un opérateur binaire, dont l'exécution par le processeur POP conduit à l'affectation de la valeur de <expression> au champ INDEX du mot de contrôle du fichier.

### III.- LES ENTREES/SORTIES EVOLUEES

Le programmeur dispose de deux fichiers séquentiels prédeclarés, les fichiers INPUT et OUTPUT, qui correspondent respectivement à un "fichier-carte" et un "fichier imprimante". Le langage PASCAL donne la possibilité d'utiliser des procédures d'entrée/sortie évoluées sous la forme suivante:

#### III.1. La procédure READ(<variable>)

Cette procédure commande d'abord la lecture de la carte suivante, puis la recherche sur cette carte d'une constante symbolique de même type que la <variable>, et enfin l'affectation de la valeur de la constante symbolique à la <variable>.

Cette procédure complexe du langage PASCAL ne peut pas être directement interprétée par microprogrammation, par le fait qu'elle fait intervenir tous les processeurs de la machine PASCALE et surtout par le fait qu'un ordre d'entrée/sortie doit être émis vers le système.

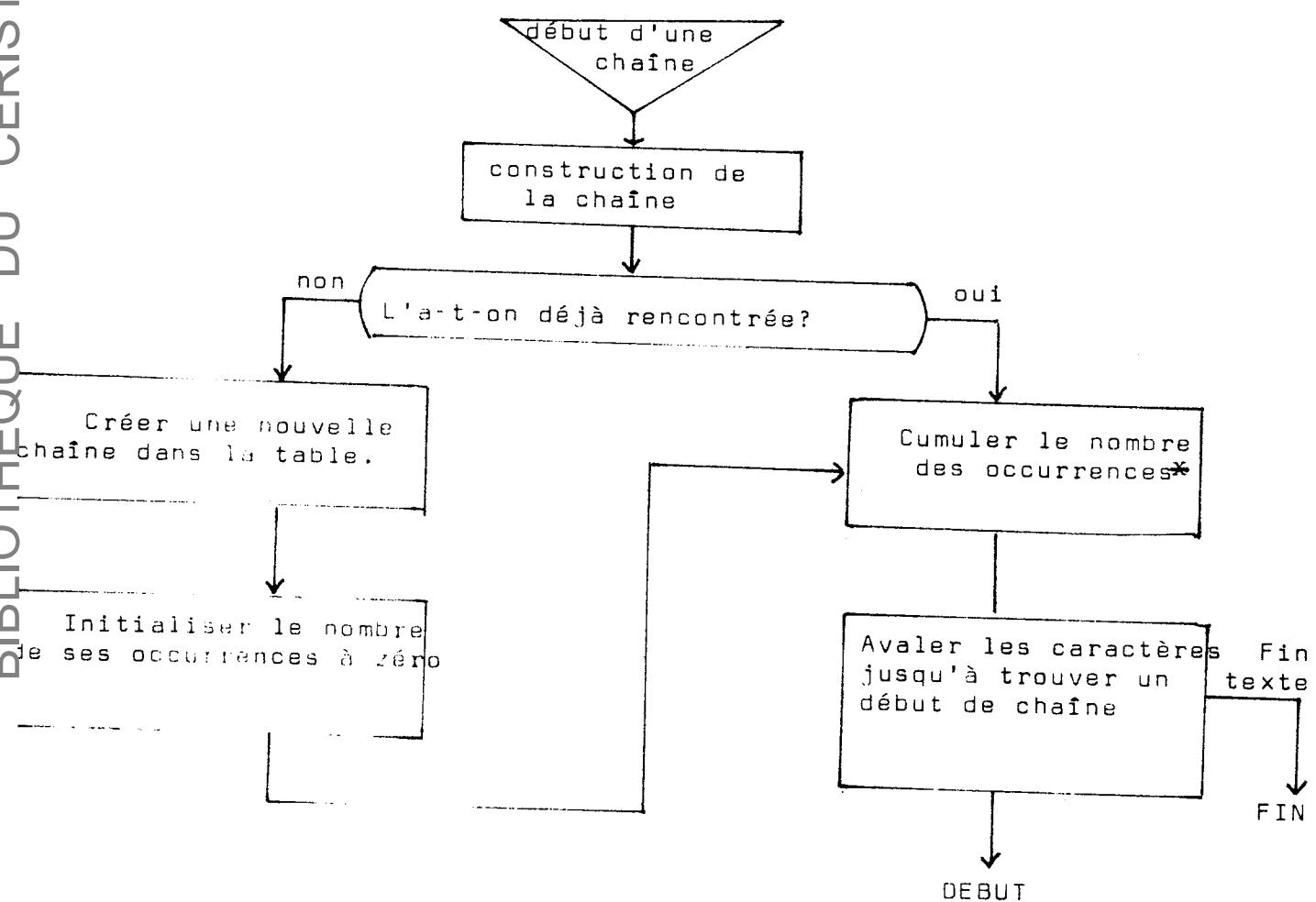

Sa réalisation est donc programmée en langage-machine et les diverses procédures qui la réalisent sont des points d'entrée dans le module externe que nous appellerons BIBLIOTHEQUE DU SYSTEME.

Les diverses procédures correspondent aux différents types de constantes symboliques qui peuvent apparaître sur une carte et qui sont:

| <u>type de constante</u> | <u>nom de la procédure</u> |

|--------------------------|----------------------------|

| entier                   | READINT                    |

| réel                     | READREAL                   |

| booléen                  | READBOOL                   |

| scalaire                 | READSCAL                   |

| caractère                | READCHAR                   |

| ensemble scalaire        | READSETSCAL                |

| ensemble entier          | READSETINT                 |

| chaîne                   | READALFA                   |

Toutes les procédures précédentes sont appelées avec un paramètre par référence. Leur déclaration est par exemple:

procédure READINT (var N : integer) ;

et la programmation de READ(T[I+1]) est équivalente à celle de

READINT(T[I+1])

qui est compilé en:

```

CALL-EXT #READINT

NOM T

NOM I

SUCC

INDEX

PARAM-EXT SP,-3

ENTER-EXT #READINT

```

L'écriture de ces procédures est faite une fois pour toutes par les programmeurs-système, qui disposent de deux variables prédéfinies appelées NIMPUT et NOUTPUT, qui donnent respectivement la position dans la carte lue et la position dans la ligne écrite pour les deux fichiers prédéfinis INPUT et OUTPUT. Ces deux variables sont implantées à deux adresses fixes en tant que variables globales (noms(0,0) et (0,1)).

### III.1.1. la procédure READINT

La première instruction est un appel au système: on lui demande la lecture de la carte suivante. Le pointeur NINPUT est initialisé à ZERO et on recherche la première occurrence d'une constante entière (suite de chiffres décimaux). La constante entière trouvée est rangée dans la variable SYMB, qui est de type "chaîne de caractères", puis on programme l'affectation du symbole SYMB au paramètre N.

N := SYMB ;

Lors de l'exécution, le processeur POP reçoit un ordre d'affectation d'une chaîne de caractères (variable SYMB) à une variable entière (N).

La conversion "chaîne de caractères" → "valeur entière" est microprogrammée dans le processeur POP qui exécute une séquence de multiplications par 10 selon l'algorithme:

```

N := 0;

for I := 0 to L ;

N := 10*N + SYMB[I]

```

où L est la longueur de la chaîne de caractères.

La multiplication par 10 est exécutée en 2 microinstructions:

$$\begin{array}{ll} 1/ (N+N)*2 \rightarrow M & \Rightarrow M = 4*N \\ 2/ (M+N)*2 \rightarrow N & \Rightarrow N = (4*N + N)*2 = 10*N \end{array}$$

On réalise ainsi une très bonne performance pour cette conversion, en faisant un compromis entre la programmation et la microprogrammation.

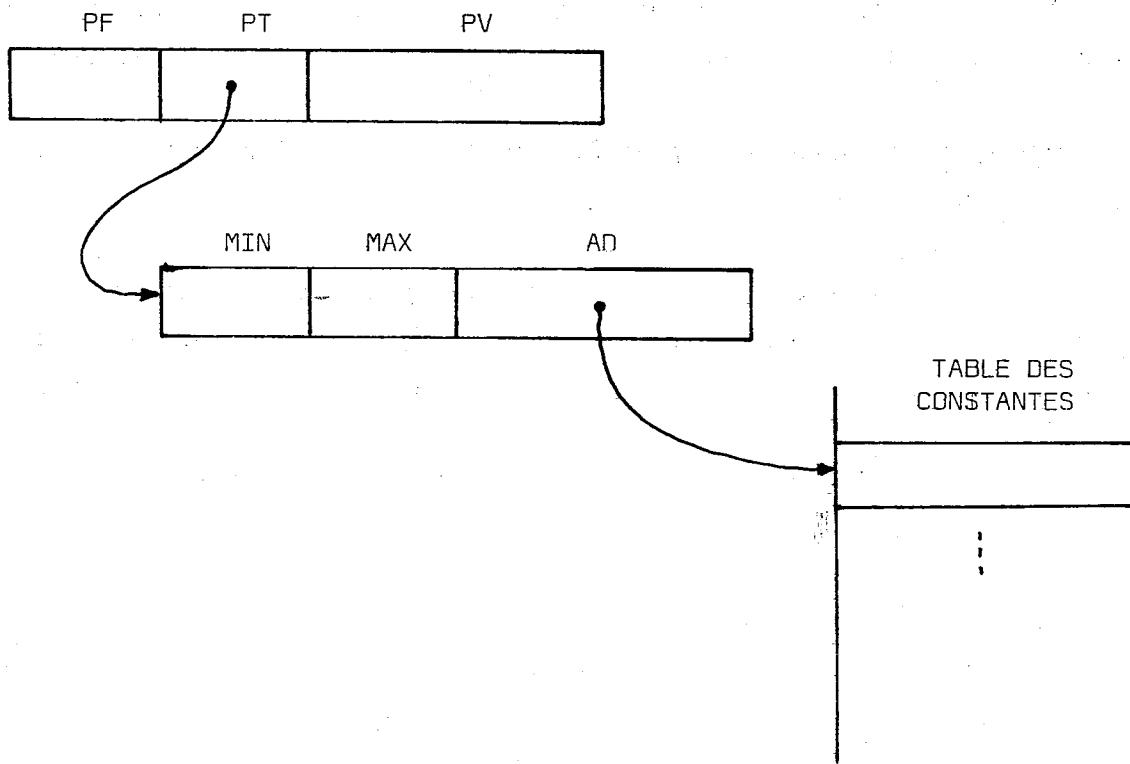

#### II.1.3. la procédure READSCAL

Un scalaire symbolique se présente comme un identificateur (chaîne de caractères commençant par une lettre et limitée à 8 caractères).

La procédure accède au symbole et la conversion "chaîne de caractères" → "valeur scalaire" est microprogrammée dans le processeur POP.

##### Réalisation de cette conversion:

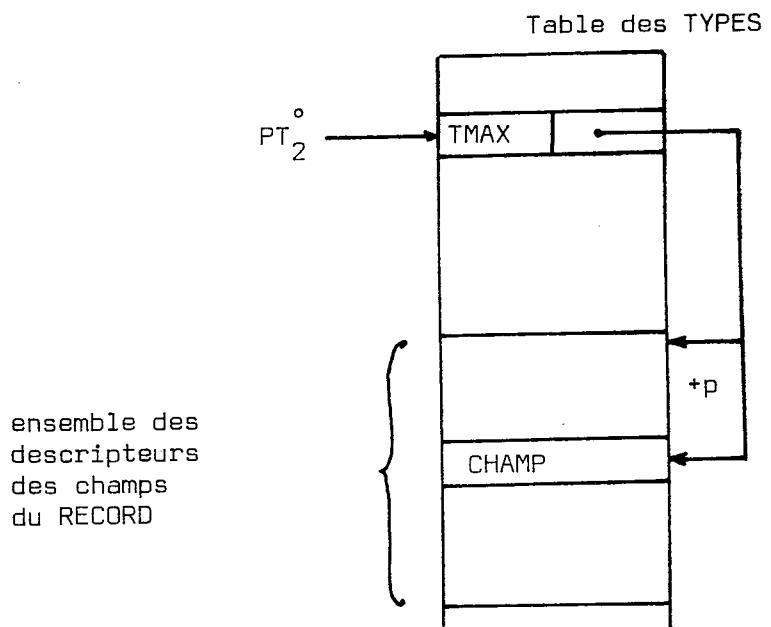

Rappelons que le descripteur d'une variable de type scalaire contient l'adresse d'un descripteur de type scalaire, qui lui-même contient l'adresse de la première constante symbolique dans la table des constantes. Cette structure est donnée par la figure .

La conversion consiste en une recherche du symbole lu sur la carte dans la table des constantes. Cette conversion est microprogrammée:

- accès au descripteur de type,

- recherche dans la table des constantes,

- affectation du numéro d'ordre du symbole à la variable de type scalaire.

En cas d'échec dans les comparaisons, le processeur POP émet un message d'erreur vers le système.

### III.1.5. la procédure READSET

Cette procédure vérifie la syntaxe d'une constante représentant un ensemble sur une carte:

[<constante>, <constante>, ...]

Lorsqu'une constante a été trouvée, elle est mise dans SYMB et l'instruction S := S UNION SYMB permet d'ajouter un élément à l'ensemble, sachant que la conversion "chaîne de caractères" → "valeur scalaire" est microprogrammée et exécutée par le processeur POP lors de l'accès au deuxième opérande de l'opérateur UNION.

### III.2. La procédure WRITE (<expression>: <longueur>)

Le programmeur dispose d'une procédure d'impression prédeclarée sur le fichier-imprimante prédéfini.

Elle lui permet de commander l'impression de la valeur d'une <expression>, en spécifiant une <longueur> d'impression (nombre total de caractères).

Le type de l'<expression> peut être n'importe quel type simple: entier, réel, scalaire...

Comme les conversions sont faites par microprogrammation et qu'il n'y a pas de problèmes de reconnaissance d'une syntaxe comme sur la carte d'entrée, tous les ordres d'écriture pourraient être réalisés par une seule procédure externe, appelée WRITE qui aurait pour paramètre une <expression> de type quelconque et la <longueur> d'impression.

Malheureusement, les problèmes de formatage sont propres à chaque type simple: par exemple un entier est "cadré" à droite, une chaîne de caractères est "cadrée" à gauche. Pour cette raison, nous avons, comme dans le cas de la procédure READ, défini autant de procédures externes que de types simples, ce qui présente l'avantage de résoudre le problème du type du paramètre de ces procédures.

| type de l'expression | nom de la procédure |

|----------------------|---------------------|

| entier               | WRITINT             |

| réel                 | WRITREAL            |

| booléen              | WRITBOOL            |

| scalaire             | WRITSCAL            |

| caractère            | WRITCHAR            |

| ensemble scalaire    | WRITSETSCAL         |

| ensemble entier      | WRITSETINT          |

| chaîne               | WRITALFA            |

Toutes les procédures précédentes sont compilées une fois pour toutes dans le module externe appelé BIBLIOTHEQUE du SYSTEME. Comme pour les procédures de lectures évoluées, un compromis a été trouvé entre la programmation et la microprogrammation: la conversion "expression" → "chaîne de caractères" est microprogrammée (affectation SYMB := valeur), alors que le formatage sur la ligne de sortie est programmé.

Exemple:

```

procédure WRITINT (N: integer; L: 1..100);

var SYMB: array [0..11] of CHAR ;

begin SYMB := N ; ← conversion microprogrammée

/* le résultat est cadré à droite dans SYMB */

puis rangement de SYMB, avec troncation ou extension à gauche,

end ;

```

Remarque: La conversion "valeur entière" → "chaîne de caractères" est microprogrammée dans le processeur POP. L'algorithme de conversion suppose une succession de divisions par 10, dont les restes donnent les chiffres successifs en partant des plus faibles poids, ce qui facilite le cadrage à droite.

Il n'existe pas, à notre connaissance, de méthode simple de division d'un nombre binaire par 10, alors que nous avons donné une méthode de multiplication par 10 en 2 microinstructions (cf. III.1.1. du même chapitre). Une étude a cependant été faite pour réaliser la division par 10 à l'aide d'une succession de divisions par 8. Elle consiste à décomposer le résultat de la division par 8 de la manière suivante:

$$N = 8 * Q_8 + R_8$$

est écrit sous la forme  $N = 10 * Q_8 + (R_8 - 2 * Q_8)$ . On fait  $Q_{10} \leftarrow Q_8$  et on pose  $D_8 = R_8 - 2 * Q_8$ .

Si  $D_8$  est compris entre 0 et 9, alors  $D_8$  est bien le reste de la division par 10. Sinon, on fait une nouvelle division par 8 et on obtient:

$$D_8 = 10 * Q'_8 + (R'_8 - 2 * Q'_8).$$

On ajoute  $Q'_8$  à  $Q_{10}$  et on pose de nouveau

$$D'_8 = R'_8 - 2*Q'_8.$$

On recommence ainsi jusqu'à trouver un dividende  $D_8$  compris entre 0 et 9.

Cet algorithme est performant pour un dividende petit:

- 1 pas pour  $10 \leq N \leq 15$

- 2 pas pour  $16 \leq N \leq 19$

- 1 pas pour  $20 \leq N \leq 23$

mais il faut par exemple 7 pas pour  $N = 28341$

| $D_8$                | $Q_8$ | $R_8$ | $Q_{10}$ partiel    |

|----------------------|-------|-------|---------------------|

| 28341                | 3542  | 5     | 3542                |

| -7079                | -885  | 1     | 2657                |

| 1771                 | 221   | 3     | 2878                |

| -439                 | -55   | 1     | 2823                |

| 111                  | 13    | 7     | 2836                |

| -19                  | -3    | 5     | 2833                |

| 11                   | 1     | 3     | 2834                |

| $R_{10} \rightarrow$ | 1     |       | $\leftarrow Q_{10}$ |

Sachant que chaque pas peut nécessiter un nombre important de cycles (environ 8 cycles), il vaut mieux utiliser l'algorithme classique de division qui nécessite 16 cycles quelle que soit la grandeur du dividende.

### III.3. les procédures WRITELN et READLN

Ce sont des cas particuliers des procédures WRITE et READ qui spécifient que l'écriture ou la lecture se font sans changer de ligne ou de carte.

On ajoutera donc un paramètre booléen à chaque procédure READ ou WRITE qui spécifiera cette condition.

### IV.- CONCLUSION SUR LES ENTREES/SORTIES

La machine PASCALE étant avant tout une machine-langage destinée à l'exécution de programmes, nous avons réduit le traitement des entrées/sorties au minimum, c'est-à-dire à la conversion de données symboliques en données codées, en laissant le soin au système d'exploitation "hôte" de résoudre les problèmes de gestion et d'accès aux périphériques.

Cependant, il faut remarquer le compromis "programmation-microprogrammation" trouvé dans la réalisation des entrées-sorties évoluées: toutes les conversions sont microprogrammées, ce qui représente un avantage considérable sur une machine classique dans laquelle elles sont programmées.

CHAPITRE 2PRESENTATION GENERALE DE L'ARCHITECTURE de PASC-HLL

- A - DEFINITION DU CODE-MACHINE

- B - MECANISME D'INTERPRETATION

## A - DEFINITION D'UN CODE MACHINE ADAPTE A LA COMPILEMENT ET A L'EXECUTION DES LANGAGES DE HAUT NIVEAU A STRUCTURE DE BLOCS (ET SPECIALEMENT PASCAL).

Tout ordinateur est défini, en grande partie, par son code machine dont les caractéristiques influent grandement sur les performances des programmes (facilité d'écriture, concision des programmes, encombrement des programmes exécutables, fiabilité software, rapidité d'exécution). Dans le cas précis qui nous concerne d'une machine langage, le concepteur a l'avantage de connaître le langage de haut niveau qu'il aura à compiler et peut choisir un code machine adapté à la compilation puis à l'exécution des programmes compilés. Les critères de choix de ce code machine sont complexes et font appel à deux notions principales qui s'avèrent être étroitement liées entre elles:

- la première notion est celle de compaction du code généré. En effet, un programme "réside" sur des supports d'information généralement coûteux (disques, bandes ...) et ne passe qu'une infime partie de sa "vie" en mémoire centrale. On a donc tout intérêt à obtenir des programmes exécutables de plus faible encombrement possible, pour réduire les coûts de "résidence" en mémoire secondaire et les temps de transfert en mémoire centrale.

Comment peut-on compacter un programme?

Une instruction étant constituée par un code opération et des opérandes, la taille d'une instruction pourra être optimisée en réduisant la taille des opérandes et leur nombre. Sachant que les instructions les plus fréquentes réfèrent une (ou plusieurs) variable(s), on cherche à définir un espace d'adressage minimum pour ces variables.

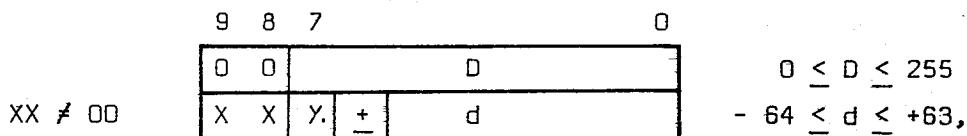

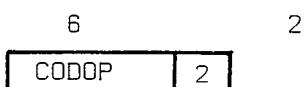

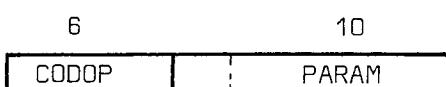

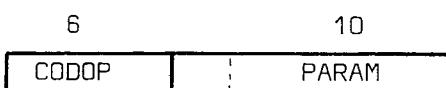

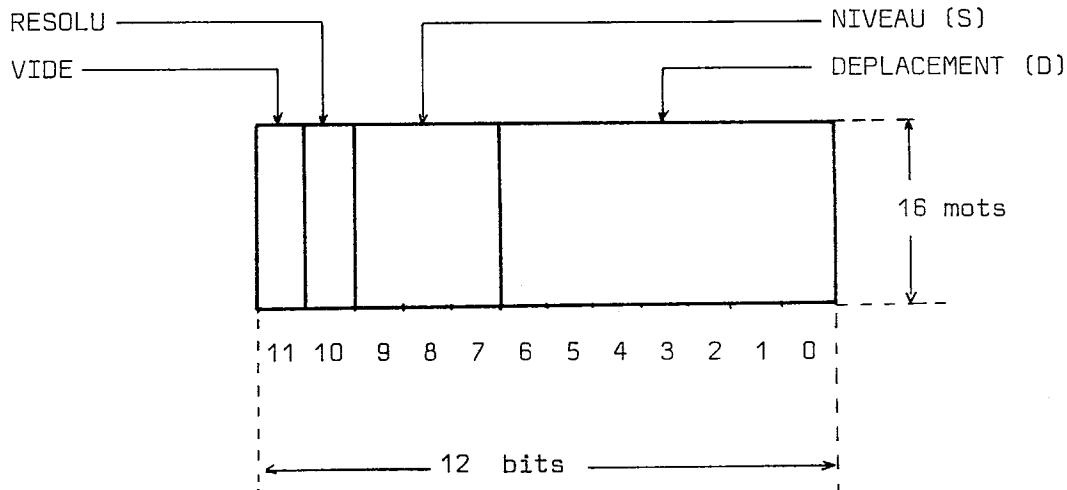

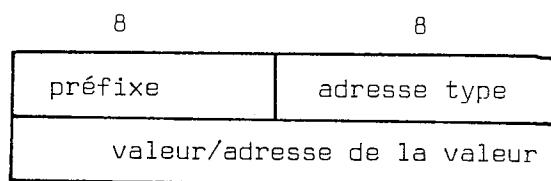

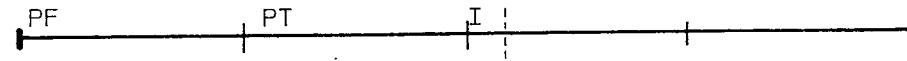

Concrètement, dans le cas d'un langage à structure de blocs, des mesures sur des programmes ont montré qu'il était suffisant de pouvoir référencer jusqu'à 256 variables dans le bloc principal, et jusqu'à 64 variables et 64 paramètres dans les blocs (ou procédure) intermédiaires. D'autre part, en ce qui concerne le langage PASCAL, une imbrication statique des procédures pouvant aller jusqu'à 6 niveaux est suffisante. En conséquence, l'espace d'adressage des variables d'un programme peut être limité à 10 bits, en spécifiant un niveau lexicographique et un déplacement de la manière suivante:

Cette compaction de l'adresse d'un opérande permet de réduire à 16 bits la taille des instructions d'accès aux opérandes (6 bits pour le code opération et 10 bits pour le couple (niveau, déplacement)).

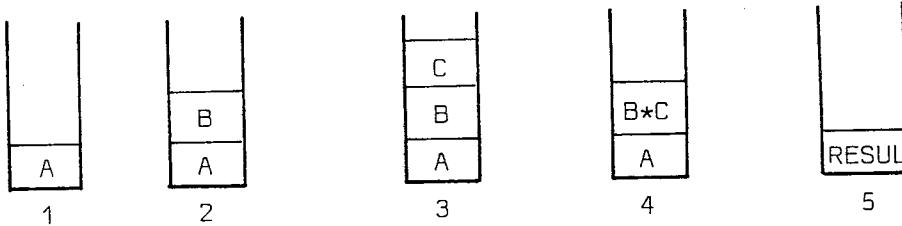

Une deuxième solution pour réduire la taille d'une instruction est de limiter le nombre de ses opérandes explicites, en définissant des opérandes implicites. Cette réduction est obtenue en choisissant par exemple un code machine de structure post-fixée ou polonaise , dans laquelle apparaissent seulement deux types d'instructions qui sont les instructions d'accès à un opérande dont l'adresse est explicite et des opérateurs (unaires ou binaires) dont les opérandes sont implicites.

exemple:

|                        |                      |

|------------------------|----------------------|

| l'expression A + B * C |                      |

| est compilée en        | Accès A    2 octets  |

|                        | Accès B    2 octets  |

|                        | Accès C    2 octets  |

|                        | *            1 octet |

|                        | +            1 octet |

|                        | <hr/>                |

|                        | 8 octets             |

Si l'on compile l'expression précédente dans une code classique (IBM 360), on obtient dans le cas le plus favorable d'optimisation par le compilateur:

|       |           |

|-------|-----------|

| L R,B | 4 octets  |

| M R,C | 4 octets  |

| A R,A | 4 octets  |

| <hr/> |           |

|       | 12 octets |

ce qui fait déjà apparaître un facteur de compaction important, mais non significatif pour un programme complet

|                    |          |           |

|--------------------|----------|-----------|

| Sans optimisation: | L R1,A   | 4 octets  |

|                    | L R2,B   | 4 octets  |

|                    | M R2,C   | 4 octets  |

|                    | AR R1,R2 | 2 octets  |

|                    | <hr/>    |           |

|                    |          | 14 octets |

Cette première méthode de compaction a des effets sensibles mais limités, en particulier on ne pourra jamais réduire l'encombrement d'une valeur immédiate donnée. Cependant, il est possible de définir plusieurs types de valeurs immédiates. En effet, des mesures ont montré qu'environ 95% des valeurs immédiates référencées dans un programme peuvent être codées sur 8 bits, et que les constantes égales à "zéro" ou à "un" sont très fréquemment référencées. On peut donc compacter le code en introduisant les instructions suivantes:

|                         |          |

|-------------------------|----------|

| ZERO (préfixe)          | 1 octet  |

| UN (préfixe)            | 1 octet  |

| LIT8 (préfixe, valeur)  | 2 octets |

| LIT16 (préfixe, valeur) | 4 octets |

dont l'encombrement est inversement proportionnel à la fréquence d'utilisation et où le paramètre "préfixe" indique le "type" de la constante.

L'espace d'adressage des instructions peut également être étudié afin de réduire l'encombrement des instructions de branchement. En effet, tout programme écrit en langage de haut niveau est naturellement structuré, d'abord en procédures (ou blocs), puis en groupes d'instructions délimités par des instructions de test ou de boucles. Si l'on conserve cette structuration au niveau du code machine, on aboutit à la notion de segments de contrôle, qui peuvent s'imbriquer les uns dans les autres comme des blocs. On utilise alors un système d'adressage implicite qui permet de référencer implicitement soit le début, soit la fin du segment.

Exemple:

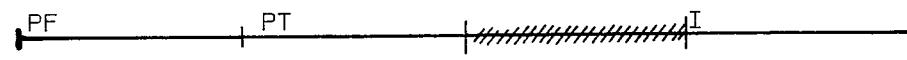

la structure while <exp> do <instruction> peut être compilée en:

LOOP (m) ←————— 2 octets

<exp>

WHILE ←————— 1 octet

<instruction>

ENLOOP ←————— 1 octet

Dans ce cas, l'instruction LOOP(m) définit le début et la fin d'un segment (par

son paramètre m). Les deux instructions WHILE et ENDLOOP référencent implicitement le début et la fin de la boucle et peuvent être codées sur seulement 8 bits. Dans un code classique, on aurait généré deux instructions BRANCH, codées chacune sur 4 octets.

On remarque, sur cet exemple, un facteur 2 pour la réduction de l'encombrement statique, et un facteur 4 pour l'accès dynamique aux instructions au cours de l'exécution: en effet, quand on "tourne" dans la boucle, seules les instructions WHILE et ENDLOOP sont accédées en mémoire centrale où elles n'occupent que deux octets au lieu de 2 instructions BRANCH qui occupent 8 octets.

- la deuxième notion importante pour la définition d'un code machine "compact" concerne la puissance des instructions, ou plus précisément leur aptitude à exprimer les notions sémantiques complexes contenues dans le langage de haut niveau. Le problème consiste à trouver, pour chaque notion sémantique évoluée, un ensemble d'instructions minimum qui soit cependant suffisant pour que la machine puisse, éventuellement en plusieurs étapes, exécuter toutes les opérations nécessaires à la réalisation de cette notion évoluée. Là encore, la compaction des instructions est obtenue en définissant des opérandes implicites et des structures de données évoluées, spécialement définies en fonction de leur utilisation par des instructions compactes.

Nous donnons ici plusieurs exemples d'application de cette notion.

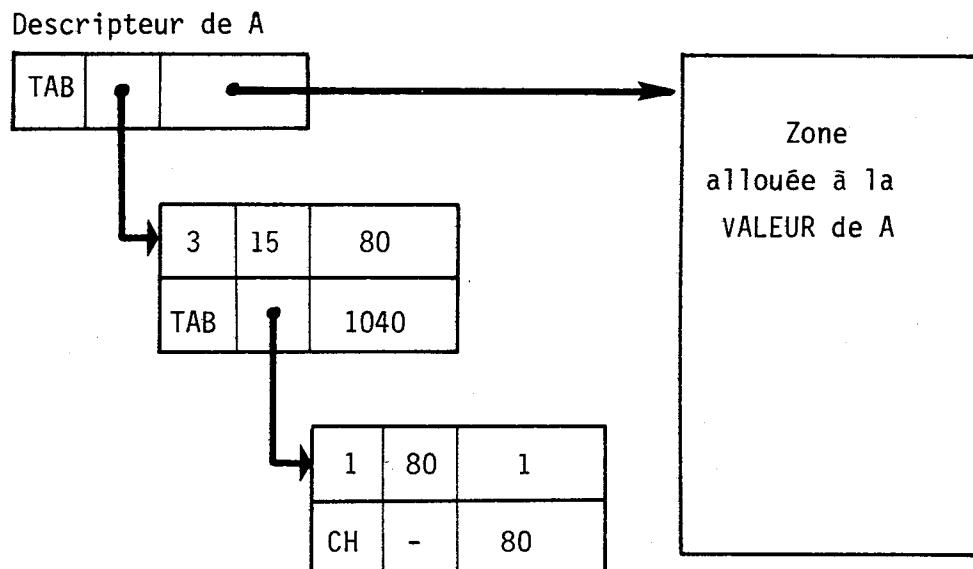

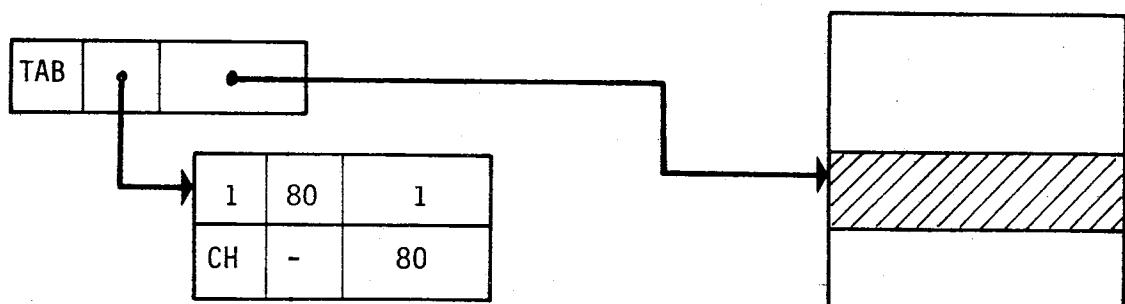

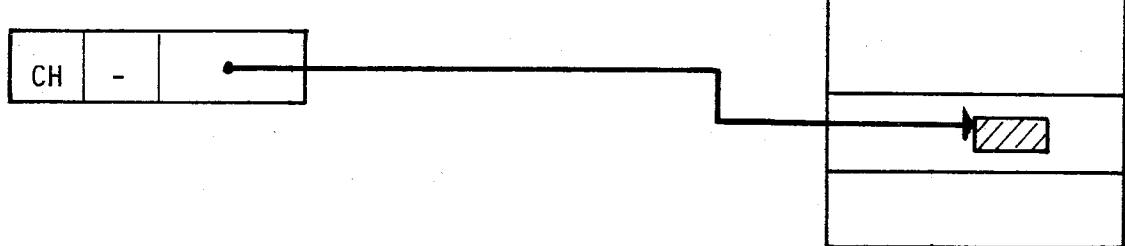

Examinons d'abord le cas bien connu de l'INDEXATION d'un tableau, déclaré par exemple par:

```

type TAB = array [3..15] of array [1..80] of CHAR ;

var A, B, C : TAB ;

```

Les trois variables A, B et C sont de type TAB, qui définit un tableau à deux dimensions dont les éléments sont de type "caractère" et occupent chacun 1 octet.

Dans un code classique, une référence à un élément du tableau, par exemple A[I,J] est compilée en:

4 LA R<sub>3</sub>, adresse de A

4 LA R<sub>0</sub>, adresse courante

4 L R<sub>1</sub>, borne sup de A (=15)

2 CR R<sub>1</sub>, R<sub>4</sub> R<sub>4</sub> contient l'INDEX I

1° 4 BH erreur

dim 4 L R<sub>1</sub>, borne inf de A (=3)

2 SR R<sub>1</sub>, R<sub>4</sub>

4 BL erreur

4 M R<sub>1</sub>, pas de A (=80)

2 AR R<sub>3</sub>, R<sub>1</sub> R<sub>3</sub> contient l'@ de A

LA R<sub>0</sub>, adresse courante

L R<sub>1</sub>, borne sup de A (=80)

CR R<sub>1</sub>, R<sub>5</sub> R<sub>5</sub> contient l'INDEX J

BH erreur

2° dim 4 L R<sub>1</sub>, borne inf de A (=0)

SR R<sub>1</sub>, R<sub>5</sub>

BL erreur

M R<sub>1</sub>, pas de A (=1) inutile

AR R<sub>3</sub>, R<sub>1</sub>

et toutes ces instructions sont nécessaires si l'on veut vérifier que l'index est bien compris entre les bornes inférieure et supérieure.

Sans cette vérification on obtient:

|     |                                    |   |

|-----|------------------------------------|---|

|     | LA R <sub>3</sub> , adresse de A   | 4 |

|     | L R <sub>1</sub> , borne inf       | 4 |

| 1°  | SR R <sub>1</sub> , R <sub>4</sub> | 2 |

| dim | M R <sub>1</sub> , pas de A        | 4 |

|     | AR R <sub>3</sub> , R <sub>1</sub> | 2 |

|     | <br>                               |   |

|     | L R <sub>1</sub> , borne inf       |   |

| 2°  | SR R <sub>1</sub> , R <sub>5</sub> |   |

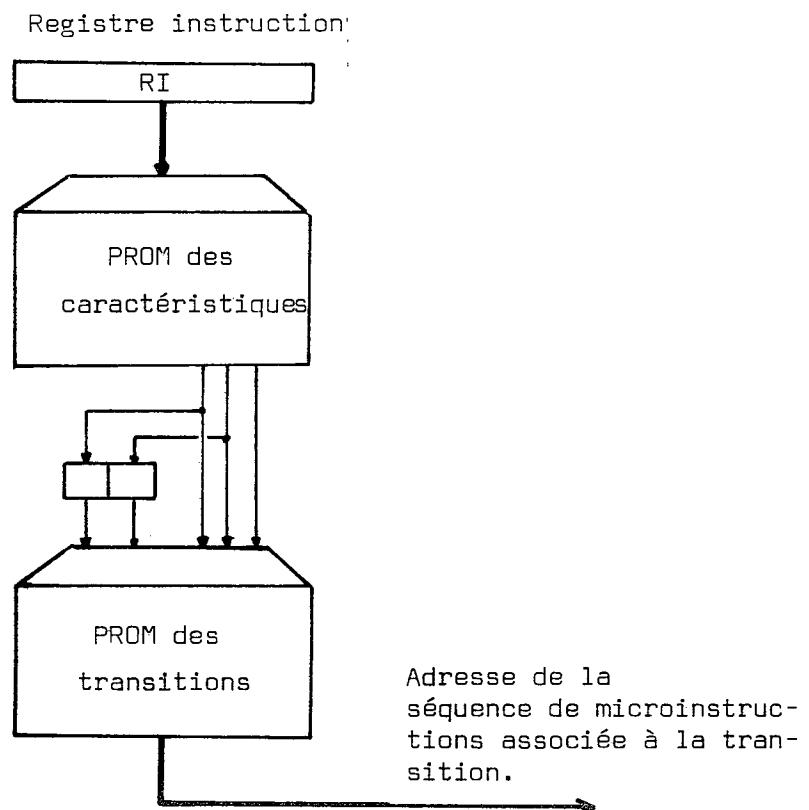

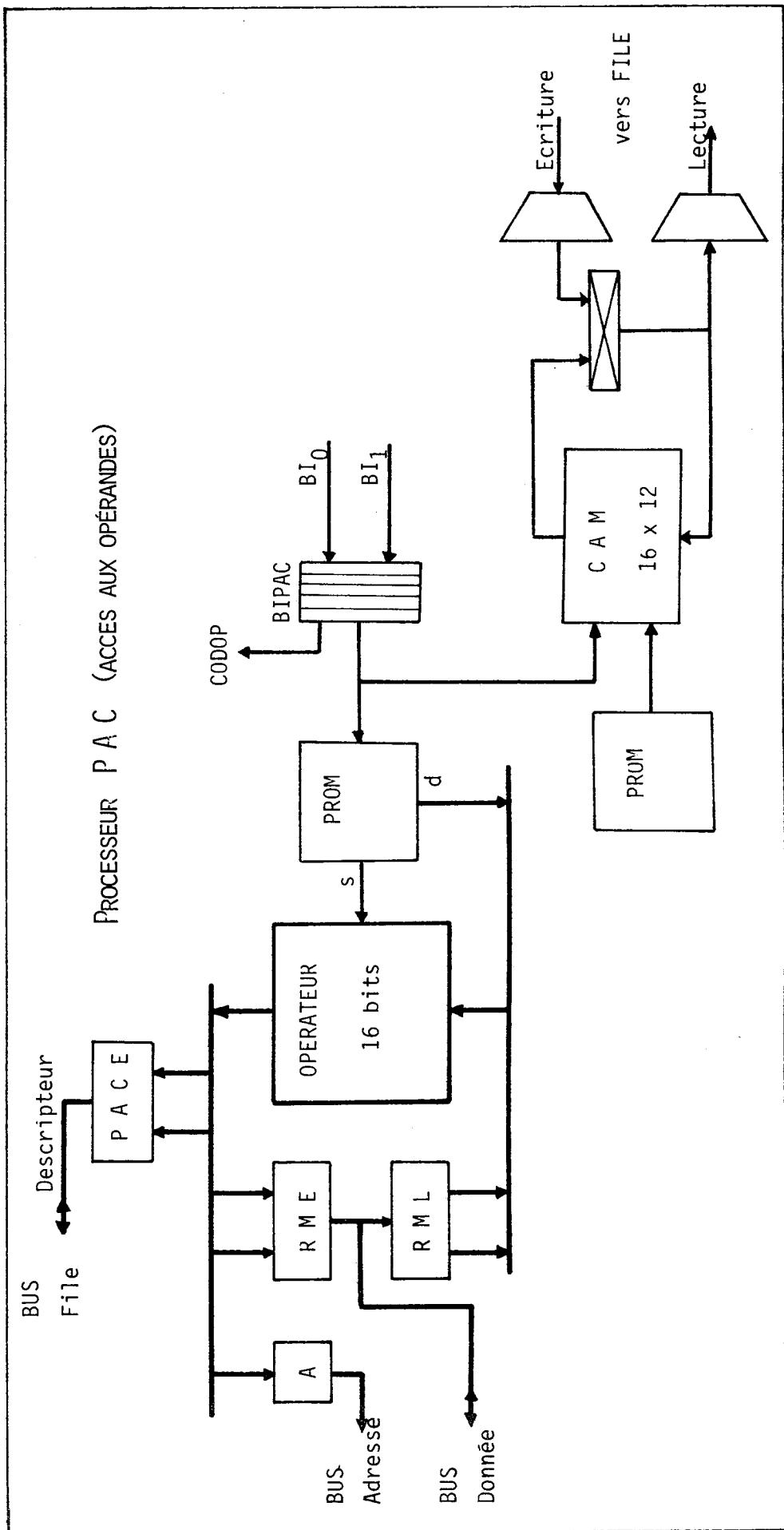

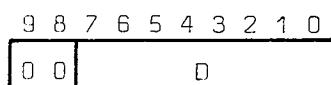

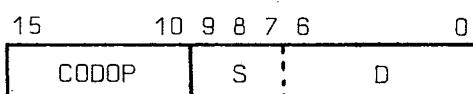

| dim | AR R <sub>3</sub> , R <sub>1</sub> |   |